This is a joint work from Universities of L’Aquila, Sassari and Cagliari. It presents the demo and tutorial of JOINTER, a framework that allows to develop complex heterogeneous architectures composed of programmable processors and dedicated reconfigurable accelerators on FPGA, together with customizable monitoring systems, keeping under control the introduced overhead.

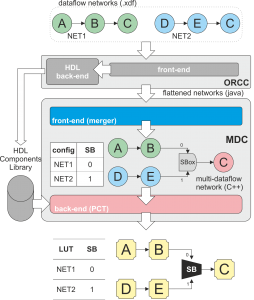

The Multi Dataflow Composer Tool

Universities of Sassari and Cagliari are developing Multi Dataflow Composer Tool which automatically generate runtime reconfigurable hardware platforms. MDC, starting from a set of applications described as dataflow models, is able to generate a multi-functional dataflow specification embedding all the given input ones and, then, to assemble the reconfigurable system capable of correctly executing them one at a time.

Visit GitHub or website for download and details.

And there are video tutorials on YouTube.

Meeting in Prague (March 2020)

Meeting in Valencia (December 2019)

Meeting in Eindhoven (September 2019)

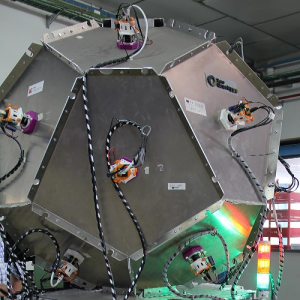

Online Quality Control with 360° Inspection System

ITI is creating an innovative inspection system that uses 360° 3D Artificial Vision techniques for online quality control. This solution will be easy to integrate into the production process and allows real-time capture, 3D reconstruction and inspection of each part while it is in free fall, without any contact, manipulation or concealment. The main goal in this project is to increase performance of data acquisition for a 3D industrial inspection system by improvements in the object detection algorithms to be run close to the cameras in a low power execution platform. This objective will be achieved by means of code parallelization and network optimization.

ITI is designing and developing two use cases for 3D industrial inspection and robotic arm calibration. In addition to that, the Institute is participating in the reference architecture, identifying all the required software and hardware components to optimize the throughput and latency of the system.

Network Scheduling for Critical Traffic

Seven Solutions aims to measure and evaluate the real time requirements and RT-QoS. Through the incorporation of Time Sensitive Networking-based techniques, Seven Solutions brings robustness and reliability to Ethernet by offering IEEE standard communication technology with mechanisms to enable the coexistence of critical and best effort data within the same network. To make these improvements, Seven Solutions will deal with bandwidth reservation for critical traffic and by using a common notion of time, Seven Solutions will provide traffic scheduling.

7SOLS has a wide expertise in timing and ultra-accurate synchronization, and Time Sensitive Networking (TSN) is a branch of activity for the company. The company is working on a hard deterministic latency TSN solution. Consequently a Time-Aware traffic Shaper scheme is followed instead of the classic tow-queue Credit-based shaper one. The study of the state of the technique in order to develop the TAS have been carried out. TSN implementation has started and first point-to-point tests are currently in progress.

Smart Camera with Embedded Object Detection

As a part of traffic surveillance use case, we integrate advanced HDR image capturing and object detection in FPGA, targeting Zynq platform in a smart camera. The camera will capture multi-exposure Full-HD video at 90 FPS and merge the image stream to 30 FPS tone-mapped HDR video using novel motion-aware merging algorithm.

In the traffic surveillance scenario we will detect license plates using our highly optimized object detector IP core. The detections along with the HDR image are made available for CPU part in order to execute other tasks like plate recognition or tracking. Such a technology will enable surveillance in challenging lighting conditions where other object detection methods often fails.

Currently our work focuses on improvements of the object detection core and its integration with the image merging algorithm and optimization of execution using event-based profiling.