#### ECSEL2017-1-737451

#### **FitOpTiVis**

#### From the cloud to the edge - smart IntegraTion and OPtimisation Technologies for highly efficient Image and VIdeo processing Systems

# Deliverable: D2.1 Component models, abstractions, virtualization and methods

Due date of deliverable: (31-05-2019)

Actual submission date: (12-06-2019)

Start date of Project: 01 June 2018

Duration: 36 months

Responsible: CUNI

Revision: final version

|    | Dissemination level                                                                   |   |  |  |  |  |  |

|----|---------------------------------------------------------------------------------------|---|--|--|--|--|--|

| PU | Public                                                                                | - |  |  |  |  |  |

| PP | PP Restricted to other programme participants (including the Commission Service       |   |  |  |  |  |  |

| RE | Restricted to a group specified by the consortium (including the Commission Services) |   |  |  |  |  |  |

| со | Confidential, only for members of the consortium (excluding the Commission Services)  |   |  |  |  |  |  |

#### **DOCUMENT INFO**

#### Author list

| Author             | Company | E-mail                      |

|--------------------|---------|-----------------------------|

| Marc Geilen        | TUE     | m.c.w.geilen@tue.nl         |

| David Millán       | ITI     | dmillan@iti.es              |

| Carlo Sau          | UNICA   | carlo.sau@diee.unica.it     |

| Tomas Bures        | CUNI    | bures@d3s.mff.cuni.cz       |

| Petr Hnetynka      | CUNI    | hnetynka@d3s.mff.cuni.cz    |

| Vaclav Camra       | CUNI    | camra@d3s.mff.cuni.cz       |

| Pablo Sánchez      | UC      | sanchez@teisa.unican.es     |

| Fernando Manteca   | UC      | mantecaf@teisa.unican.es    |

| Martijn Hendriks   | TUE     | m.hendriks@tue.nl           |

| Pablo Chaves       | SCHN    | Pablo.chaves@se.com         |

| David Pampliega    | SCHN    | David.pampliega@se.com      |

| Hossein Elahi      | TUE     | g.elahi@tue.nl              |

| Shayan Tabatabaei  | TUE     | s.tabatabaei.nikkhah@tue.nl |

| Freek van den Berg | TUE     | f.g.b.v.d.berg@tue.nl       |

| Twan Basten        | TUE     | a.a.basten@tue.nl           |

#### **Document history**

| Document<br>version # | Date       | Change                                                      |

|-----------------------|------------|-------------------------------------------------------------|

| V0.1                  | 18-10-2018 | Starting version, template                                  |

| V0.2                  | 23-4-2019  | Description of UML Marte, virtualization methods and models |

| V0.3                  | 5-5-2019   | Description of DSL and component abstractions               |

| V0.4                  | 9-5-2019   | Added mathematical component model                          |

| V0.5     | 16-5-2019 | Added introduction and reference architecture                                |  |

|----------|-----------|------------------------------------------------------------------------------|--|

| V0.6     | 27-5-2019 | Integrated changes to DSL and component model                                |  |

| V0.7     | 29-5-209  | Unified style of figures with component architecture. Fixes in DSL examples. |  |

| V0.8     | 30-5-2019 | Incorporated updates from UC and additional fixes in figure and DSL examples |  |

| V0.9     | 31-5-2019 | Complete version for internal review                                         |  |

| Sign off | 3-6-2019  |                                                                              |  |

| V1.0     | 7-6-2019  | Final version                                                                |  |

#### **Document data**

| Editor Address data | Name:    | Marc Geilen                          |

|---------------------|----------|--------------------------------------|

|                     | Partner: | TUE                                  |

|                     | Address: | De Zaale, Eindhoven, The Netherlands |

|                     | Phone:   | +31-402473091                        |

#### **Distribution list**

| Date                                         | Issue | E-mailer                             |

|----------------------------------------------|-------|--------------------------------------|

| 12-06-2019 Final fitoptivis-wp2@lists.utu.fi |       | fitoptivis-wp2@lists.utu.fi          |

|                                              |       | Patrick.vandenberghe@ecsel.europe.eu |

# **Table of Contents**

| 1. | EXECUTI                | /E SUMMARY7                                                    |  |  |

|----|------------------------|----------------------------------------------------------------|--|--|

| 2. | INTRODU                | CTION                                                          |  |  |

|    | 2.1                    | Overview of requirements8                                      |  |  |

|    | 2.2                    | Motivation                                                     |  |  |

|    | 2.3                    | Objectives9                                                    |  |  |

|    | 2.4                    | Relation to Other Work Packages                                |  |  |

|    | 2.5                    | Overview of the Document                                       |  |  |

| -  |                        |                                                                |  |  |

| 3. |                        | ICE ARCHITECTURE                                               |  |  |

|    | 3.1                    | Proposed Solution12                                            |  |  |

|    | 3.2                    | Template Solutions14                                           |  |  |

| 4. | COMPON                 | ENT ABSTRACTIONS17                                             |  |  |

|    | 4.1                    | State-of-the-Art and Related Work                              |  |  |

|    | 4.1.1                  | SYSML                                                          |  |  |

|    | 4.1.2                  | IEC 6113119                                                    |  |  |

|    | 4.1.3                  | IEC 6149919                                                    |  |  |

|    | 4.1.4                  | AADL                                                           |  |  |

|    | 4.1.5                  | KOALA20                                                        |  |  |

|    | 4.1.6                  | PROCOM20                                                       |  |  |

|    | 4.1.7                  | FRACTAL (THINK AND MIND)21                                     |  |  |

|    | 4.1.8                  | SOFA 2 AND SOFA-HI                                             |  |  |

|    | 4.1.9                  | BLUEARX21                                                      |  |  |

|    | 4.1.10                 | AUTOSAR22                                                      |  |  |

|    | 4.1.11                 | UML-MARTE22                                                    |  |  |

|    | 4.1.12                 | MATHEMATICAL COMPONENT MODELS                                  |  |  |

|    | 4.1.12.1               | Behaviour Interaction Priority BIP                             |  |  |

|    |                        | Contract-based frameworks                                      |  |  |

|    | 4.1.12.3<br><b>4.2</b> | Basic terminology and definitions                              |  |  |

|    | 4.3                    |                                                                |  |  |

|    |                        | Detailed description of the reference architecture model 28    |  |  |

|    | 4.3.1<br>4.3.2         | BLACK-BOX VIEW                                                 |  |  |

|    | 4.3.2<br>4.3.3         | COMPONENT CONFIGURATIONS                                       |  |  |

|    | 4.3.3<br>4.3.4         | EXAMPLE: COMPONENT ABSTRACTION IN VR USE CASE                  |  |  |

|    | 4.3.4<br><b>4.4</b>    |                                                                |  |  |

| F  |                        | Mathematical Component Framework for Quality and<br>lanagement |  |  |

|          | 4.4.1              | COMPONENT FRAMEWORK DEFINITION                            | 35   |

|----------|--------------------|-----------------------------------------------------------|------|

| 5.<br>AB | DOMAIN<br>STRACTIC | SPECIFIC LANGUAGE FOR THE COMPON                          |      |

|          | 5.1                | Example                                                   | 40   |

|          | 5.2                | Specification                                             | 43   |

|          | 5.2.1              | IMPORT                                                    |      |

|          | 5.2.2              | BUDGET INTERFACE DEFINITION                               | 44   |

|          | 5.2.3              | CHANNEL INTERFACE DEFINITION                              |      |

|          | 5.2.4              | COMPONENT DEFINITION                                      |      |

|          | 5.2.4.1            | Interface usage predicates                                |      |

|          | 5.2.5              | PROPERTY PREDICATES                                       |      |

|          | 5.2.6              | SUBCOMPONENT PREDICATES                                   | 47   |

|          | 5.2.7              | CONSTRAINT PREDICATES                                     | 48   |

|          | 5.2.7.1            | And-predicate                                             | 48   |

|          | 5.2.7.2            | Or-predicate                                              | 48   |

|          | 5.2.7.3            | Implication-predicate                                     | 49   |

|          | 5.2.7.4            | Runs on / Outputs to predicates                           | 49   |

|          | 5.2.8              | EXPRESSIONS                                               | 49   |

|          | 5.2.8.1            | Inline arrays                                             | 50   |

|          | 5.2.8.2            | Inline objects (composite values)                         | 50   |

|          | 5.2.9              | BOOLEAN EXPRESSIONS                                       |      |

|          | 5.2.9.1            | Comparison expressions                                    | 51   |

|          | 5.2.9.2            | In-expression                                             |      |

|          | 5.2.10             | QUALITY EXPRESSIONS                                       | 51   |

|          | 5.2.11             | SYSTEM                                                    | 52   |

| 6.       | VIRTUAL            | IZATION MECHANISMS                                        | 53   |

|          | 6.1                | Introduction                                              | 53   |

|          | 6.2                | State-of-the-Art                                          | 53   |

|          | 6.2.1              | VIRTUALIZATION MODELS                                     |      |

|          | 6.2.2              | VIRTUALIZATION FOR QUALITY AND RESOURCE MANAGEM           |      |

|          | -                  | 57                                                        |      |

|          | 6.3                |                                                           | 59   |

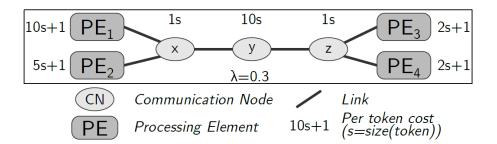

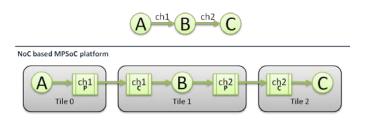

|          | 6.3.1<br>COMPSOC   | EXAMPLE INSTANCE: VIRTUAL PLATFORM MODELS C60             | IN   |

|          | 6.3.2<br>SPIDER    | EXAMPLE INSTANCE: VIRTUAL PLATFORM MODELS IN PREE 61      | ESM/ |

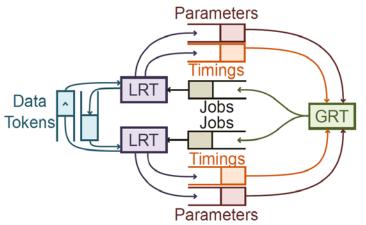

|          | 6.4                | Quality and Resource Management Conceptual Architec<br>61 | ture |

|          | 6.4.1<br>IN COMPS  | EXAMPLE INSTANCE: QUALITY AND RESOURCE MANAGEM            |      |

6.4.2 EXAMPLE INSTANCE: QUALITY AND RESOURCE MANAGEMENT IN SPIDER 63

| 7.  | INSTANC          | ES OF THE REFERENCE ARCHITECTURE                                                   |

|-----|------------------|------------------------------------------------------------------------------------|

|     | 7.1              | Component Abstractions for Multi-Source Streaming 65                               |

|     | 7.2              | Component Abstractions for an Industrial Inspection System 70                      |

|     | 7.3              | Model-based component abstraction73                                                |

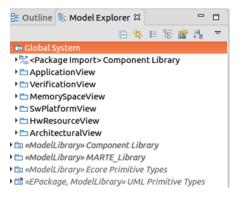

|     | 7.3.1            | COMPONENT MODELLING IN UML-MARTE75                                                 |

|     | 7.4              | Component Abstractions for Time Sensitive Networks 78                              |

| R   | 7.5<br>Redundanc | Component Abstractions for High-availability Seamless y in Remote Terminal Units80 |

|     | 7.6              | Component Abstractions for People Tracking System 81                               |

|     | 7.7              | Component Abstractions for Action Recognition83                                    |

| 8.  | CONCLUS          | SIONS                                                                              |

| 9.  | REFEREN          | ICES                                                                               |

| 10. | APPEN            | DIX A GRAMMAR OF THE DSL91                                                         |

#### 1. Executive summary

This report represents Deliverable D2.1 and documents the outcomes of the activities in WP2, Tasks 2.1 (Component Abstractions) and 2.2 (Virtualization Mechanisms) of the FitOpTiVis project during the first year of the project, starting from M4. The main objective of this deliverable is to establish the first version of the *reference architecture* to be used in the activities and use cases of the project. A conceptual architecture is introduced that describes the common elements in the work developed in the project. It provides *template solutions* that require further detailing and specialization for the individual use cases and application domains.

A component abstraction is defined with which platform and application components developed in the project can be uniformly *modelled* in terms of a defined set of *interfaces*. The intention of this abstraction is to define the common aspects only, and to position them in a common architecture but to leave room for domain-specific refinements to be made to specialize models, architectures and methods for the individual developments in the project.

Virtualization mechanisms are introduced pertaining to the architectural concepts and the modelling of virtual resources and their abstract budgets to achieve predictable and composable application behaviour and resource reconfiguration options. The methods of implementing virtualization in hardware and/or software are subjects of WP4.

The content of this deliverable contributes to achieve MS3 (Preliminary components and methods release with standalone assessment).

### 2. Introduction

### 2.1 Overview of requirements

In this section we describe the driving requirements of FitOpTiVis on the component abstractions.

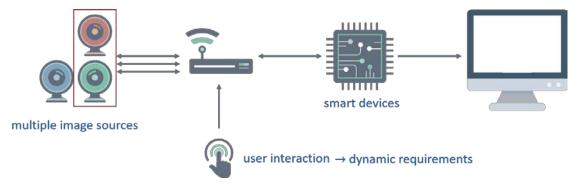

The main purpose of the FitOpTiVis component model is to define video processing pipelines out of hardware and software components and to facilitate quality and resource management for such pipelines. The goal of the component model is to allow design space exploration and run-time adaptation. As such, the **component model should allow associating configuration parameters with components** (such as supported resolution, fps, etc.) and **allow reasoning about dependencies of these configuration parameters across components** (both hardware and software) in the pipeline.

The component model is going to be applied on new components, but also on existing components where the intellectual property protection does not allow detailed modeling of the internals of the component. As such the **component model should provide hierarchical abstractions** that allow a large scale from very fine-grained components (on the level of data processing tasks) to coarse-grained components (on the level of devices with embedded software).

The component model should be used by partners in the project and other scientific and industrial users that have no extensive background in component modeling or component-based architectures, as such the **component model should be easy to use**. This in particular means that it should **provide only constructs that are needed in the project and that the semantics of the constructs should be tailored to the needs and the domain of the project**. Additionally, the **component model should have textual notation**, which simplifies sharing the models and working with the models. This is facilitated with the introduction of a DSL.

#### 2.2 Motivation

WP2 addresses Objective 1 of the FitOpTiVis project.

**Objective 1**: Template solutions for: component abstractions (covering video and imaging tasks and heterogeneous processing, storage and network devices and components); virtualization supporting scalability, portability and composability principles; multi-objective quality and resource management (support for run-time decision making, adaptation, (re-) distribution and upgrades).

Image and video pipelines will be detailed into a reference architecture and a virtual platform consisting of abstract components. The architecture and models will emphasize multi-objective optimisation including performance and energy. The use cases will be built on top of a concrete version of the reference architecture.

The use cases, component applications and platforms in the project span a wide range of technologies, methods and tools. It is not possible to build a single integrated

hardware, software and tooling framework in which all activities are integrated, nor would this be desirable, since different domains have and need their specialized models, methods, tools, and hardware, software and middleware platforms.

The range of use cases and technologies in the project share common solutions and principles that are being explored and developed in the project. Those solutions and principles can be applied across many of the separate domains. These common solutions can only be effectively identified and developed when the individual developments are positioned within a shared framework, architecture and established common models and abstractions.

In this deliverable, we establish the first iteration of such solutions and principles in the form of a reference architecture and template solutions that capture the essential concepts and the common approach. A component abstraction is introduced that characterizes the aspects of components that are deemed most important to explicitly expose in FitOpTiVis. Those aspects are their input and output streams, their provided and/or required resource budgets, the configurations they support and the aspects of quality or cost that can be optimized.

# 2.3 Objectives

The main goal for this deliverable may be stated as follows.

Goal: establish a common reference for component abstraction and the concept of a virtual platform. The reference architecture will be provided in the form of template solutions for a flexible virtual platform built from the component abstractions and offering multi-objective run-time optimisation support for quality and resource management.

To realize this goal, the deliverable pursues the following objectives.

- [Section 3] Provide a reference architecture for the FitOpTiVis innovations. Introduce the common conceptual elements in the image and video pipeline systems of FitOpTiVis and their inter-relations.

- [Section 4] Provide a common component abstraction that describes the main aspects of the elements from which FitOpTiVis systems are built and provide a compositional model in which components can be composed into applications, platforms and systems.

- [Section 4.5] Provide means to model multi-objective quality and resource optimization and management (support for run-time decision making, adaptation, (re-) distribution and upgrades).

- [Section 5] Provide template solutions to define abstract components (covering video and imaging tasks and devices and components) using a domain-specific language (DSL).

- [Section 6] Provide virtualization mechanisms supporting scalability, portability and composability principles.

- [Section 7] Evaluate the reference architecture and template solutions for selected domain specific approaches and systems.

## 2.4 Relation to Other Work Packages

This section summarizes the relations between the work in WP2 and the work reported in this deliverable and other work packages and their deliverables.

#### • WP1, Requirements and validation and result analysis

WP1 defines the use cases that are used to validate all project results. WP2 will explicitly consider the requirements derived from the use cases, in particular, the various types of components used in the cases and the quality metrics used to evaluate them.

Deliverables D1.1 and D1.2 provide the detailed specifications of the use cases and requirements. This includes the components, the optimization metrics and relation to project Objective 1, the use of the reference architecture.

#### • WP3, Design-time support

WP3 will develop model-based design-time methods with concrete models that are instances of the generic component abstraction in the template solution of WP2. The concrete design methods provide, besides the devices and components that are efficient, functional, etcetera, also the necessary information as required by the WP2 component abstractions and interfaces. Deliverable D3.1 provides first versions of the design-time optimization, deployment and programming strategies that will be aligned with the reference architecture in follow up steps.

#### • WP4, Run-time support

WP4 will implement middleware and platform components that conform to the virtualization and quality and resource management approach (developed in WP2) of the FitOpTiVis reference architecture as instances of the template solution for run-time management.

Deliverable D4.1 provides preliminary run-time models and support for energy, performance and other qualities. In subsequent steps, monitoring techniques will be used to provide an online view of the system status from the perspective of the reference architecture and its component model, e.g., the set points in which components are operating, their quality metrics, virtual platforms and budget allocations.

#### • WP5, Devices and components

WP5 will develop high-performance, energy-efficient processing and communication devices and components that conform to the reference architecture. Their development specifically considers the key aspects that characterize components in the component model, reconfiguration, qualities, inputs, outputs and budgets. Human and machine-readable descriptions of the components are made using the DSL (Domain Specification Language) introduced in this deliverable that enables automated processing of the components at design-time or run-time.

Deliverable 5.1 Components Analysis and Specification presents an analysis of the state-of-the-art of existing components for computation and networking. The inventory will be used to validate the proposed component abstractions to see if the properties and configurations of such components can be (accurately) modelled and the construction of systems from such components can be compositionally determined from the component models.

#### • WP6, Use Cases and demonstrators

The template solutions of the FitOpTiVis reference architecture developed in WP2 will be used in the demonstrators planned in WP6 for the project use cases. Domain-specific and or use-case specific solutions will be shown, but they will be shown to be instances of a common architecture and to exhibit common principles and solutions.

#### 2.5 Overview of the Document

The remainder of the deliverable is structured as follows. Section 3 introduces the reference architecture and the proposed solutions for the FitOpTiVis project, including the way it is envisioned to present template solutions. Section 4 presents the component abstractions that are used in the project to characterise the various platform and application components with which the project activities will be dealing. It includes a discussion of the literature, a conceptual model and a mathematical model that allows a precise abstraction and a framework to express multi-objective optimization goals. Section 5 defines the domain specific language for component models. (A full definition is given in Appendix A.) Section 6 discusses the conceptual modelling virtualization mechanisms, virtual platforms and quality and resource management architecture. Section 7 shows initial modelling efforts to validate the reference architecture and component abstractions currently defined.

# **3. Reference Architecture**

## 3.1 **Proposed Solution**

The FitOpTiVis project considers a wide diversity of platforms, resources, applications, methods, tools and objectives. One could not aim for one solution to fit all needs and concerns simultaneously. It is important that commonalities between the approaches and use cases are found and exploited such that reusable results can be achieved and can be applied across different domains and use cases.

The FitOpTiVis project addresses the concern of diversity by the definition of a *reference architecture* that captures what is common to the use case of the project and to the domain of image or video pipelines for CPS on a heterogeneous network spanning the cloud to the edge. Individual use cases and individual developments in the project will consider their specialized version and additional detail, but they will be positioned with respect to the framework of the reference architecture to identify common problems and solutions and to ensure consistency and they can leverage the framework.

The proposed solution includes the following ingredients.

- A *reference architecture* is defined that captures the common assumptions and approaches in the project. The use cases will be positioned in terms of the elements of the reference architecture.

- A common *component abstraction* is defined that represents a shared abstract view of platform and applications components establishing their properties. It includes an abstract component model and compositions that build system models. The model focuses on aspects of data streams (re)configuration, virtualization, heterogeneity, resource sharing and (multi-objective) quality. It is anticipated that specialized application domains in the project have their own domain-specific refinements in the form of more detailed or additional models, but that these are consistent with the architecture.

- As the detailed models are domain-specific, likewise, the various solutions developed in the project will be diverse and domain-specific, whether they are run-time methods, design-time method, virtualization techniques, etcetera. The project intends to identify common solutions and general patterns of solution strategies in the form of *template solutions*, which are reusable elements amenable to be applied in different contexts.

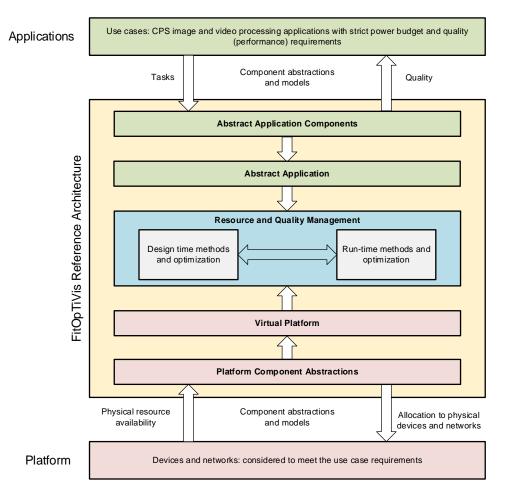

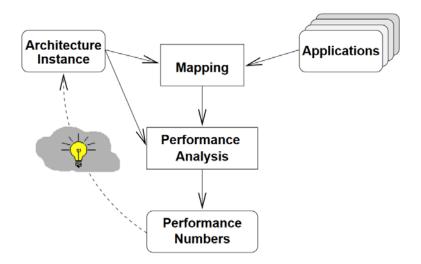

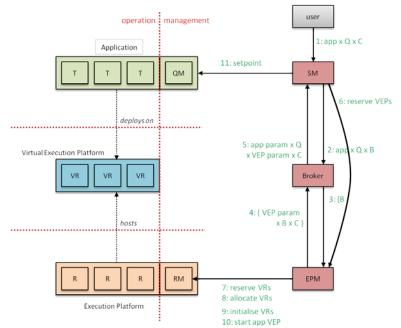

The project defines a reference architecture as a common reference for component abstraction and the concept of a virtual platform. The overview of the reference architecture is visualized in Figure 1. More precise definitions are given in Section 4.3—4.5.

Figure 1: FitOpTiVis Reference Architecture

The top side shows concrete applications and the bottom side the concrete platform of a system under consideration. The reference architecture is concentrated in the yellow box between them. It deals with abstractions of applications and platform. Applications are considered as a collection of tasks. Applications can be potentially configurable at design-time reconfigurable at run-time. They are considered to have alternative configurations or set points that are explicit in the architecture model. We do not insist that all applications are (re)configurable. Some applications may have a trivial set of configurations, or just a single possible configuration. In general, configurations are characterized by different workloads on the execution platform and different quality provisions to the user of the application (for example, power consumption or latency). Different configurations are associated with a set of application parameters. In the framework, application tasks are modelled as application components, and the collection of applications components of an application are referred to as an *abstract application*.

The platform (bottom) side is abstracted as a virtual platform. It is assumed to be (re)configurable and resources can, in general, be shared by different applications. This does not mean that in all possible instances resources shall be shared by multiple applications. Resource virtualization is a particular emphasis of the FitOpTiVis project

and the architecture likewise assumes that resources provide virtual resources to applications in the form of a *virtual execution platform*.

The abstract applications and the abstract virtual platforms are brought together by a resource and quality management framework. This framework is responsible for finding feasible and optimal combinations of applications and platforms, and for finding the optimal set points of the components. The combinations need to match, which requires both application models and platform models have appropriate models of their resource requirements and resource provisions, respectively. As illustrated in the figure, part of this optimization work is done at design-time when components are designed and developed, and part of this work may be done at run-time when more information may be available, but less time to take and enforce any decisions.

We anticipate that large differences may exist in how the resource and quality management is implemented and executed in different domains, but the expected common approaches are captured in the architecture.

#### 3.2 Template Solutions

The project intends to identify common solutions and general patterns of solution strategies in the form of template solutions, which are reusable elements amenable to be applied in different contexts. We identify what solutions are investigated and formulate initial concepts in this deliverable. They will be further detailed and evaluated in the project.

The project will specifically pursue the following classes of template solutions.

- The common conceptual model of the *component abstraction* itself. It is introduced in detail in Section 4. It defines what elements are commonly expected to be defined and how they are related. It also defines how components are composed into systems and how requirements on compositions are expressed, for instance the satisfaction of requirements, compatibility of inputs and outputs, and matching provision and requirements of resource budgets.

- A *domain-specific language* (DSL) that provides a human and machine-readable version of the abstract component models, their compositions and quality- and resource management requirements and objectives. The language supports the evaluation of completeness, uniformity and consistency of the many specific models that are made in the project. It also allows automation and tool support for common analysis and synthesis techniques (such as visualization or code generation) or model transformations. Detailed components in the project should be supplemented with a manifest description in this DSL. An initial version of this DSL is introduced in Section 5.

It is anticipated that some of the specific application domains and use cases in the project will develop their own, specific refinements of the DSL in a 'domain-specific DSL' or 'DSDSL'.

• A precise, *semantics of the component abstraction* is given in terms of a mathematical description of components and their composition operators. The composed system is provided with a semantics in terms of the constraints on the combined collection of configuration parameters and matching inputs and outputs, and well-defined multi-objective optimization objectives based on

ordering of budgets and qualities. The precise details of composition operators are expected to be domain specific. The overall problem of configuration, mapping and selection of set points can be captured in terms of a multi-objective constrained optimization problem. Conceptually and possibly in prototype experiments, generic constraint solving algorithms may be applied to find optimal solutions. It is expected however, that such solutions are insufficient in practice and domain-specific solutions and heuristics should be employed to determine good solutions in practice. The semantics is elaborated in Section 4.

- A virtual platform model that defines how resources and their sharing are modelled through virtual resources that are provided by virtualization mechanisms in their implementation. This allows, ideally, resources to be shared by multiple applications while providing well-defined resource budgets, to the individual applications and providing support for (re)configuration of virtual resources and their resource budgets. The virtual platform model is elaborated in Section 6.3.

- A *quality and resource management* (QRM) architecture describes how the required information, activities and responsibilities, such as optimization, monitoring, configuration, calibration, resource management, may be divided between different elements of the architecture and between design-time and run-time activities. The QRM architecture is introduced in Section 6.4.

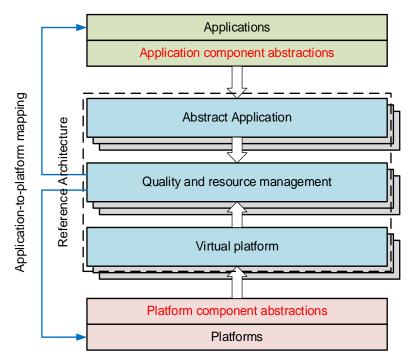

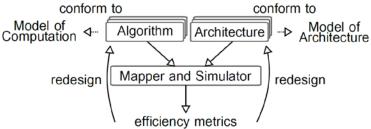

Figure 2: FitOpTiVis Template Solutions

Figure 2 illustrates how the reference architecture and template solutions are instantiated in different, more refined incarnations for different application domains. The definition of the reference architecture facilitates the relation to the work in other work packages as follows.

- WP3 develops *model-based design-time methods* with concrete models (grey) that are consistent with the generic component abstraction of the template solution (blue) of WP2. Ideally tool chains produce descriptions of the abstract component models automatically.

- WP4 creates *run-time management* solutions (grey) that are in line with the template quality and resource management (blue) laid down in WP2.

- WP5 creates (re)configurable devices and components (grey) and their component abstractions that are instances of the template solution (blue) of WP2

- WP6 demonstrates that detailed solutions in the 10 use cases.

The reference architecture and its template solutions are not expected to be directly used on any specific design problems or in any specific domain, use case or demonstrator. Instead, we expect the architecture and templates to be instantiated and specialized for a particular domain.

Specialized component models may be used that best characterize the application and or platform components that are common in a particular domain, such as timed dataflow models for real-time streaming data processing, or UML state diagrams for component-based, control-oriented software components.

Similarly, it is expected that different domains employ their own, specialized budget descriptions, specialized composition operators, specialized specification languages, mapping strategies, optimization strategies, and so forth.

Also, every domain typically has its own favoured analysis, and design-space exploration tools and methods and synthesis strategies.

We expect that the different use cases in the FitOpTiVis project will each use such a specialization of the architecture and solutions, but that they will all respect the overall architecture, which means in particular that they will follow the component model outlined in Section 4 and use the common DSL of Section 5, or a specialization thereof to model the system components. The applicability of the architecture to the various use cases should serve as a validation of the core concepts in the architecture.

## 4. Component Abstractions

In this section, we overview the basic component abstractions used in FitOpTiVis. We present the conceptual model and we introduce a mathematical model.

Though in the software engineering community and literature the "component" may refer to many different things, it is typically used in the sense of "a constituent part" of a system. For example, the UML 2 defines "component" as an entity with the following properties [OMG2017b]:

- A Component represents a modular part of a system that encapsulates its contents and whose manifestation is replaceable within its environment.

- A Component is a self-contained unit that encapsulates the state and behaviour.

- A Component specifies a formal contract of the services that it provides to its clients and those that it requires from other Components or services in the system in terms of its provided and required Interfaces. As such, a component serves as a type, whose conformance is defined by these provided and required interfaces (encompassing both their static as well as dynamic semantics).

- A Component is a substitutable unit that can be replaced at design-time or runtime by a Component that offers equivalent functionality based on compatibility of its Interfaces. As long as the environment is fully compatible with the provided and required Interfaces of a Component, it will be able to interact with this environment.

- A Component has an external view (or "black-box" view) by means of its publicly visible Properties and Operations.

- A Component also has an internal view (or "white-box" view) by means of its private Properties and realizing Classifiers i.e. internal architecture typically consisting of internal composition of components.

In FitOpTiVis, we follow this generally accepted view of a component and see a component as an abstraction of a hardware/software subsystem. We also identify important quality properties that are relevant to the FitOpTiVis subject matter of *quality and resource management* and make it possible to attach them to components or their constituents (interfaces in particular). This makes it possible to:

- reason, at *design-time*, about a system as of a composition of components and their configurations. This makes it possible to predict the overall properties of the system before the system is actually built.

- to relate, at *run-time*, monitored properties of a system to its constituents and thus to reason, still at run-time, about the system and to be able to adapt some of its parameters.

Compared to the traditional software engineering view of a component, the important distinction in FitOpTiVis is that the project takes a systems view, where a component can be realized by hardware, software or both. This makes it possible to describe a large span of options ranging from DSPs, FPGAs, to processing performed by GPU-accelerated cloud VMs (Virtual Machines) and containers.

Another important distinction of FitOpTiVis is its focus on quality and resource management. Related to this and to the fact that the hardware and software components

can be combined is that it provides both (1) a data processing workflow view (i.e., the steps in the video processing pipeline) and (2) the deployment architecture (i.e., that a software component runs on a particular hardware component).

In order to perform the design-time exploration and run-time adaptation, the component abstractions in FitOpTiVis need to allow for specification of configuration options and quality properties (along with budgets and costs).

The component abstractions are traditionally represented by a component model, which defines the component structure and meta-data and the component composition mechanism. In this section, we provide such a component model – called the *FitOpTiVis component model*. In Section 5, we then describe the textual representation (i.e., a domain specific language – DSL) that we developed for defining the components.

#### 4.1 State-of-the-Art and Related Work

In this section we analyze several existing related components models on how they approach the FitOpTiVis requirements on the component abstractions. Based on this analysis, we build the component abstractions and bring them together as the FitOpTiVis component model and the DSL to describe them (as described further in this section and Section 5).

### 4.1.1 SysML

The Systems Modeling Language (SysML)<sup>1</sup> [OMG2017a] is a dialect of the Unified Modeling Language (UML) [OMG2017b]. Since its origins it has evolved into a standard for the Model-Based Systems Engineering (MBSE) applications. As such, it aims to unify all the various documents that are created during different stages of the software engineering process into a single document used by architects, developers, domain experts and maintainers alike. Therefore, it contains structures to allow all these various groups to express their view on the system.

Compared to UML, SysML removes Activity diagrams, Block definition diagrams and Internal block diagrams. On the other hand, it adds the Requirement diagrams, which provide modeling constructs for text-based requirements, and the parametric diagrams, which describe constraints among the properties associated with blocks. The parametric diagrams could be used to express various constraints, relations of qualities and the configuration parameters of described components. Importantly, the SysML allows description of both the software and hardware components and allocation of the former ones to the latter ones.

In relation to requirements of FitOpTiVis, SysML provides means for describing most of the required parts (components, their composition, etc.). However, having a significantly broader scope, it is cluttered with many concepts that are not necessary for the FitOpTiVis objectives, which makes it very difficult to use by partners. Similarly, the lack of precise semantics makes it difficult to directly use SysML for automatic design

<sup>&</sup>lt;sup>1</sup> https://sysml.org/

space exploration and for run-time adaptation. Also, SysML **primarily uses graphical notations only** and the textual representation, which is based on XMI (XML Metadata Interchange), is intended for serialization only. This further decreases flexibility and leanness in design as opposed to the DSL descriptions we intend to use.

# 4.1.2 IEC 61131

The IEC 61131<sup>2</sup> is a microcontroller architecture standard made by the International Electrotechnical Commission. It has support for CPU instructions, functions (made from CPU instructions), sensor and actuator interfaces, human-machine interfaces, power-supply interfaces, and communication interfaces.

For our use case, it provides inspiration for components, and for specifying inputs and outputs. It has **no support for specification of configurable component quality properties** that could be used in design exploration and run-time adaptation of quality and resource aspects. Also, it does **not explicitly support hierarchical composition**.

#### 4.1.3 IEC 61499

The IEC 61499<sup>3</sup> standard is an extension of the IEC61131 (Section 4.2.2) standard for distributed industrial automation systems. It adds support for event-based processing and composition of function blocks.

Like the IEC 61131 it lacks support for component configurations and quality properties needed for design exploration and run-time adaptation. Unlike IEC 61131, it does allow for the composition of function blocks.

## 4.1.4 AADL

The Architecture Analysis & Design Language (AADL)<sup>4</sup> [FGH2006] has been introduced in 2004 by Society of Automotive Engineers as a modeling language for model-based description and analysis of complex systems in terms of interactions of components. The AADL language does not limit design description to software components, but it covers also description of computational platform elements (e.g., processor or memory) and mapping of software components to hardware.

In AADL, components are divided into three main categories: (i) Application components, which are software components such as processes, threads, subprograms, (ii) Execution platform components, which are hardware components (e.g., processor, memory), and finally (iii) Composite components (also called systems) composing other components together (both hardware and software). Component interfaces (also called features) can be of several types – for data and event passing, method calls, and direct data access. Application components also have properties that

<sup>&</sup>lt;sup>2</sup> https://webstore.iec.ch/publication/62427

<sup>&</sup>lt;sup>3</sup> https://webstore.iec.ch/publication/5506

<sup>&</sup>lt;sup>4</sup> http://www.aadl.info/

specify them, e.g., timing properties or constrains for binding executable threads to processors. AADL offers support for modes and switching among them. A mode in AADL is a distinct configuration of a component. Mode transitions are controlled by a state machine and enabled by events defined in behavior of components. Modes can specify different configurations of component composition, different call sequences, and multiple properties of components.

AADL supports many of the features required in our project – either directly or they can be modeled in terms of existing features. However, for our needs, AADL is **too complex** and **requires rather in-depth knowledge of component concepts** and would be **hard to use by non-expert users**.

#### 4.1.5 Koala

Koala [OLK+2002] is a component framework developed by Philips and targets consumer electronics. The primary goal of Koala is to easily manage the complexity of embedded software used in consumer electronics and to handle the large diversity of such devices. The component model of Koala is heavily inspired by Microsoft's COM and Darwin [MK1996] component models. Koala offers hierarchically composed components and in addition to the primitive and composite components Koala also defines modules. A module is a basic compositional unit and from an implementation view, it corresponds to a single source code file. To handle diversity of devices, Koala offers diversity interfaces and switches. The diversity interface is a required interface intended for configuration, i.e., setting parameters. A switch is a module connecting several components together and its functionality is controlled through the diversity interface. Based on the values of the diversity interface parameters, the switch chooses which components are effectively connected.

For our needs, Koala does **not support description of hardware** components. The **quality properties along with budgets and costs would be very hard to model**.

## 4.1.6 ProCOM

The ProCOM [SVB+2008] component model distinguishes two levels of granularity -ProSys and ProSave. ProSave, the lower layer, operates with low-level passive (i.e., cannot initialize a new thread) and hierarchically structured components. Computation on this level is based on the pipes-and-filters paradigm; the functionality of the ProSave component is described as a set of services. The communication between components is realized by data ports (for passing data) and triggering ports (for passing signals). Each service contains one input port group and several output port groups. ProSys, the upper layer, describes a set of concurrent components, which are called subsystems in order to distinguish them from the lower-level ProSave components. These subsystems can run potentially on several computation hardware nodes. A ProSys subsystem is composed of a set of concurrent functionalities that can be either event driven or periodic. The only way for ProSys subsystems to communicate with each other is by sending asynchronous messages via channels. Channels are strongly typed and support multiple senders and receivers. A ProSys subsystem may be modeled as an assembly of ProSave components but can be also implemented directly or as a composition of other ProSys components. Behavior of components is formally specified by a formalism based on finite state machines.

As the Koala above, the ProCOM does **not model the hardware** components and also the **quality and budget properties would be very hard to model**.

## 4.1.7 Fractal (THINK and MIND)

The Fractal [BCL+2006] component model is a classical component model with hierarchically composed components. By itself, the Fractal is only an abstract specification and there exist multiple implementations targeting different domains. For our needs, the most related implementations are THINK [FSL+2002] and MIND<sup>5</sup>, which both of them target development of embedded systems. As they are implementations of Fractal, the components are defined by their provided and required interfaces and they can be hierarchically nested. In addition to business interfaces, the components provide control interfaces via which it is possible to manage component lifecycle, configure components, etc.

The main difference to the THINK is that MIND supports for different hardware platforms explicitly expressed using descriptors. As in case of the component models above, Fractal also lacks good support for component configurations and modelling quality and budget properties.

## 4.1.8 SOFA 2 and SOFA-HI

SOFA HI [HBP+2009] is a profile of the SOFA 2 component framework [BHP2006] for development of high-integrity real-time embedded systems. SOFA 2 has a very similar set of features as Fractal, i.e., there are hierarchical components with provided and required interfaces. In SOFA 2, the components have explicitly defined their interface and implementation. Also, the connections among components are modeled via connectors, which are considered as first-class entities. SOFA 2 allows for modelling dynamic architectures (via reconfiguration patterns); SOFA HI restricts dynamism to mode switching.

For our needs, SOFA 2 does **not model explicitly the hardware** components and as above, **quality and budget properties cannot be easily modelled**.

## 4.1.9 BlueArX

BlueArX [KRS+2009] is a component framework developed and used by Bosch. It is intended for use in automotive domain, especially in embedded devices. BlueArX focuses on the design-time component model to support constrained domains considering various non-functional requirements while providing multiple views of a developed system. BlueArX uses a common hierarchical component model. The static view defines two types of components, an atomic component, which has an implementation, and a structural component, which are composed of other atomic and/or structural components. Components have interfaces dividable into two types – import and export interfaces. Connections between interfaces are implicit based on the interface names. These connections are implemented using a special type of variables

<sup>&</sup>lt;sup>5</sup> http://mind.ow2.org/

called messages; a component specifies its message access properties in its interface description. The dynamic view consists of component scheduling specification, which contains mapping of services to periodic or event-triggered tasks and the order of services inside these tasks.

For our needs, the BlueArX does **not model hardware** components and also its **implementation is not available**.

## 4.1.10 AUTOSAR

AUTOSAR<sup>6</sup> is a software architecture for development of automotive electronic control units (ECUs). It defines composable components with explicitly defined interfaces, properties, configuration and adaptation management, etc.

For our needs, it supports (directly or indirectly) many of the required features. However, it is so closely tied to the automotive domain that it is **not easily applicable to another domain**.

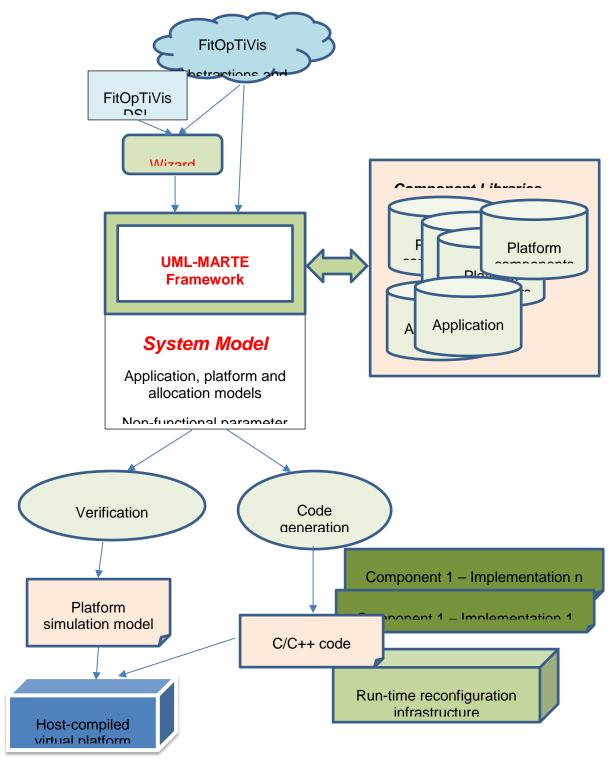

#### 4.1.11 UML-MARTE

As it has been commented in the SysML section, UML lacks the specific semantics required to fully support specification, modelling and design of current electronic embedded systems. The embedded system models need to reflect systems integrating multiple applications and diverse software platform components, e.g., embedded RTOS, middleware, drivers, etc. Similarly, current hardware architectures rely on multi-core processors, surrounded by many hardware devices for communication, storage, sensing, and actuation. In addition, several types of analysis are applied (e.g., schedulability, timed-simulations, etc.) which require to add additional information to the model, e.g., annotations of extra-functional properties related to timing, memory sizes, energy, etc. In this context, the standard MARTE profile was developed [OMG2018] to model and analyse real-time embedded systems, providing the concepts needed to describe real-time features that specify the semantics of this kind of systems at different abstraction levels.

For the needs of high-level specification MARTE is, however, **too complex**. It also **lacks simple textual notation** that would allow easy sharing of models. As such, we do not use MARTE as the first-line language, but rather, in one of the specific application domains, as a more detailed model to which specifications of some FitOpTiVis component model are translated to (see Section 7.3).

#### 4.1.12 Mathematical Component models

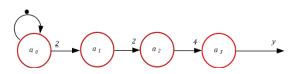

#### 4.1.12.1 Behaviour Interaction Priority BIP

To modelling heterogeneous real-time components, the BIP (Behaviour, Interaction, Priority) framework has been introduced in [BBS2006]. The lower level describes the behaviour of a component. The middle layer addresses the interaction between

<sup>&</sup>lt;sup>6</sup> https://www.autosar.org/

components. The top-level describes the scheduling information. In BIP, systems are constructed from atomic components, which are finite-state automata extended with data and ports. Data transfer is the means of interaction between components. The algebra for this interaction is presented in [BS2008].

The first version of BIP systems is static, which means that components and interactions between them are fixed at design-time. To address dynamism of a real-time system, Dy-BIP, representing a dynamic extension of the BIP framework, is introduced in [BJM+2012]. Dy-BIP offers primitives to model dynamic architectures. Transition systems are used as the atomic primitives. Transitions are labelled with ports, action names, and constraints for interaction with other components. Each atomic component provides its own interaction constraints at each computation step.

The next generation of BIP is the Dynamic Reconfigurable BIP (DR-BIP) component framework capturing three types of dynamic changes, namely, different configurations of a component, creation, and deletion of components, migrations of components between predefined architectures. The formal definition of this model can be found in [BBB+2018].

The BIP model **only considers applications as components**. Therefore, it is not able to address dynamism on the hardware side. BIP focuses primarily on **functional behaviour and interaction rather than resource usage and aspects of quality**.

#### 4.1.12.2 Contract-based frameworks

For simplicity, modularity and scalability, the design and verification should be performed at the component level. The correctness of component behaviour may depend on the behaviour of components with which it interacts. This method is referred to as *contractbased design*, because for decomposing systems into components it makes assumptions on the environment and in turn provides guarantees to the environment [CGP2008].

In their terminology, horizontal contracts are those for components at the same level of abstraction, representing different components of the system, while vertical contracts span different levels of abstraction of the same components [NSS+2012]. In contrast, the vertical relations in our terminology (see Section 4.4) refer to resource budgets between application and platform components, while horizontal composition to the exchange of data between components.

In the contract-based framework, each component has some implementations defining the behaviour of that component. These are usually deterministic and do not limit the environment. These are the main differences between contract (their component abstraction) and the implementation of a component. The guarantees of the model must be realized by an implementation. Components with contracts have an elegant compositional semantics in terms of sets of behaviours [NS2018]. When a contract guarantees more with fewer assumptions than another contract, the former is called a *refinement* of the latter. It may substitute for the former in any situation without violating any constraints. Similarly, we may consider the introduction of abstraction and refinement relations between component abstractions, for example if a component provides better qualities for less resource usage.

The contract-based frameworks provide a very generic framework but **lack the concrete syntax and support for specific constraints and compositions**. There is a **lack of tools supporting contract-based design**, except for the domain of formal verification. The contract-based frameworks do **not address dynamism** typical of reconfigurable and adaptive systems.

#### 4.1.12.3 Multi-objective optimization techniques

In many fields of study such as business, economics and engineering, one often considers two or more objectives for optimization (for example, latency and cost minimization) along with constraints on such metrics. Constraints are non-negotiable limits on some properties, while objectives are the negotiable properties. For instance, we might have a constraint on the minimum frame rate of a streaming application and would like to trade off power consumption for latency.

To find optimal solutions to multi-objective problems, one often considers *Pareto optimality*, named after economist Vilfredo Pareto. He identified solutions that helped some people (some objective metrics) without hurting anyone else (other objective metrics) [P1971]. In FitOpTiVis, we intend to use the concept of Pareto optimality and additionally explore the use of the algebraic framework introduced in [GBTO2007] for compositional reasoning about optimality of systems of components. This approach allows us to describe the design decisions for composing components either by connecting inputs and output or by matching provided and required resource budgets. The mathematical component framework for quality and resource management, introduced in Section 4.5, shows how this algebra provides functionality for component abstractions, in more detail.

#### 4.2 Basic terminology and definitions

Building on the analysis of the related work and on the experience with developing and extending various component models (ProCOM [SVB+2008], SOFA 2 [BHP2006], SOFA-HI [HBP+2009], Fractal [BCL+2006], DEECo [BGH+2013]), we define the basic abstractions of the FitOpTiVis component model as follows.

A component in the FitOpTiVis component model is the primary constituent of a system. A component can be a hardware component (e.g., a camera or a processing unit), a software component (e.g., a functional unit or a driver) or both (e.g., a smart camera). Components can have associated configuration parameters and can be composed together to form an architecture.

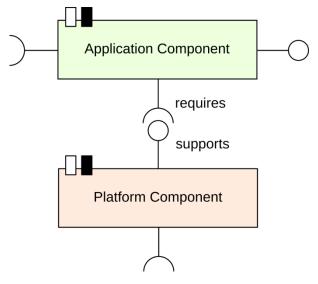

On the finest level of granularity, components can be divided to **platform components** and **application components**.

Platform components represent parts that are generic with respect to a particular application use. They provide computation means to execute actual data processing tasks. Examples of platform components include: Raspberry Pi board with Raspbian, Openstack node, a particular VM, FPGA.

Application components on the other hand represent the computation task specific to an application. Examples include: OpenCV-based routine, Docker image, routine on FPGA.

The relation between platform and application components is that an application component is hosted (runs on) on a platform component. In some cases, the same component can be both application and platform – e.g., a virtual machine component is hosted (as an application component) on an OpenStack node platform component but itself acts as a platform component for applications hosted on the virtual machine.

Application components can be connected to create data processing pipelines. Similarly, an application component may be connected to a platform component to signify the application component is hosted on the platform components.

The connection between components is realized through **bindings** between **component ports**.

Components can be **composed** to form larger components, e.g., **applications** or (virtual) **execution platforms**. In this respect, an **abstract application** is a composition of application component abstractions that provides functionality to a user. A **virtual execution platform** is a composition of virtual platform components that can run an application. An abstract application executes on a virtual execution platform, or virtual platform; a virtual platform exposes a collection of resource budgets to the abstract application. Abstract applications and virtual platforms collect all information needed for **quality and resource management**.

Components may have multiple **configurations**. A component **configuration** consists of configuration parameters (set points) that control characteristic properties of the components called **qualities**. Examples of configuration parameters include: fps, video frame resolution. Examples of qualities include: memory consumption, code size, processing speed. There are **trade-offs** between configurations and qualities – e.g., bigger video frame resolution requires more memory and leads to lower frame rate, an Openstack node can host VMs with 8GB of memory or up to twice as much VMs with 4GB of memory.

The configuration of a components (or some of its parameters) may be set at design-time (in case the configuration leads to recompilation of the component or reinstall of a component) or at run-time. The parameters that are **(re)configurable** at run-time are set via a dedicated run-time interface as developed in WP4.

An example of these component concepts is given below. We assume a smart camera component. As a black-box, this component combines both hardware and software in one package. Table 1 lists different configurations (rows). Each configuration is described by a combination of particular choice of configuration parameters (columns).

| Mode | Frame rate (fps) | Biometric<br>parameters | Faces | Raw frames |

|------|------------------|-------------------------|-------|------------|

| 1    | 1                | +                       | -     | -          |

| 2    | 1                | +                       | +     | -          |

| 3    | 1                | +                       | +     | +          |

Table 1: Smart camera component configurations.

| 4 | 10 | - | + | + |  |

|---|----|---|---|---|--|

| 5 | 10 | - | - | + |  |

| 6 | 30 | _ | - | + |  |

These example configuration options describe that the camera has selectable frame rate (1, 10, and 30 fps) and can detect biometric parameters and faces. It can also provide the entire video frame. However, only certain combinations of these parameters are possible. If for instance biometric parameters are to be provided by the camera, the frame rate is fixed to 1 reading per second.

When face detection is requested, the camera can process the video with up to 10 fps. The maximum frame rate of 30 fps is achievable only when both the detection of biometric parameters and faces is disabled.

In addition to these configuration parameters, the camera may consume different amounts of energy. Such energy consumption can be viewed as a quality parameter of the component. We assume that considering the provided features, frame rates and energy consumption, all its configurations are Pareto optimal.

For the smart camera example, frame rate, biometric parameters, faces and raw frames output are the configurable parameters that determine its set points. Frame rate and power consumption are considered its qualities.

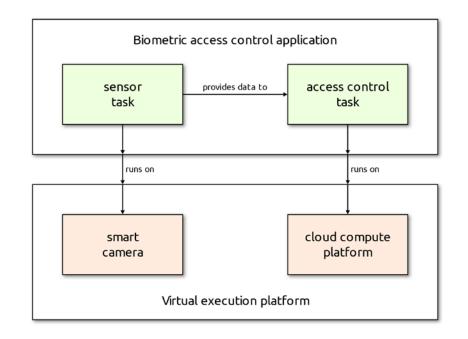

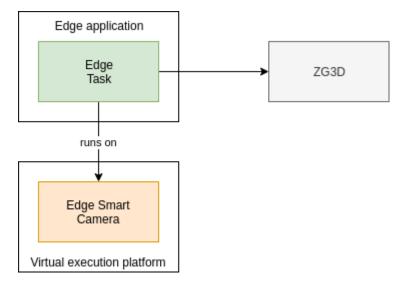

This example modeled using our component abstractions is shown in Figure 3. The architecture of the example contains two application components – *sensor task* and *control host task* – and two platform components – *smart camera* and *cloud compute platform*. The components are composed together via two principal types of bindings – "provides data to" and "runs on". In this example, the *sensor task* sends data from face recognition to *access control task*, which grants/denies physical access to identified persons. As the two tasks are application components, they need to be executed somewhere. The execution happens via a platform component. The composition of an application component with a platform component happens through the "runs on" binding. In the example below, the *sensor task* component runs on the *smart camera*, the *access control host task* runs on *cloud compute platform*.

Given the typical way of laying out the application components above the corresponding platform components, we also term the "provides data to" composition as *horizontal composition* and the "runs on" composition as *vertical composition*.

Figure 3: Example component model architecture of a biometric access application.

Application and platform components can be made at various granularities and / or hierarchically. For instance, the sensor task and the access control task can be abstracted together as the Biometric access control application. This application is in this case the top-level application component. In the same way, the smart camera and the cloud compute platform components can be abstracted as the Virtual execution platform, which is the top-level platform component.

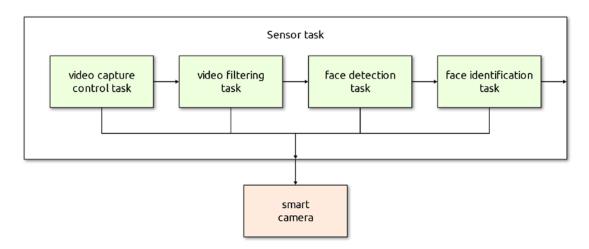

Similarly, if needed a component may be further decomposed to an architecture of finelevel components. For instance, the sensor task can be decomposed to a pipeline of 4 tasks as shown in Figure 4. Note that as the sensor task itself has two ports (one for providing data to access control task and another for being hosted on the smart camera). The sub-components inside the Sensor task delegate to these ports on the outer boundary.

Figure 4: Example of the biometric access application with decomposed sensor tasks.

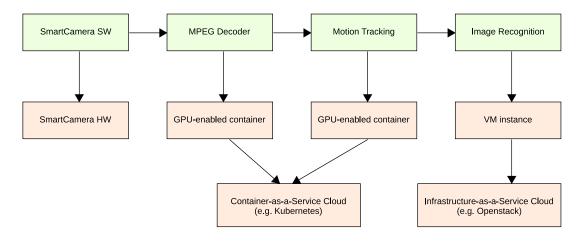

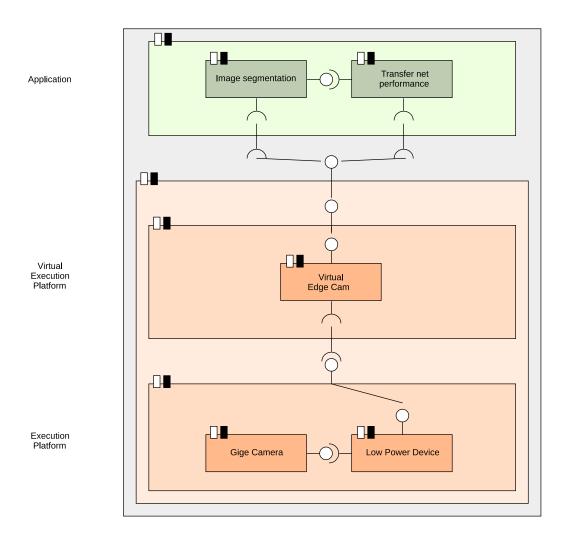

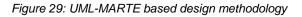

Components may also include any number of vertical layers as shown in Figure 5. The example depicts a pipeline that does part of the video processing in the cloud. Here the presence of the cloud creates two layers of platform components as the container/VM instance is virtualized on top of the cloud.

Figure 5: Example of a model with multiple platform layers.

## 4.3 Detailed description of the reference architecture model

The main constituent of the FitOpTiVis component model is the component. The component has a black-box and white-box view.

#### 4.3.1 Black-box view

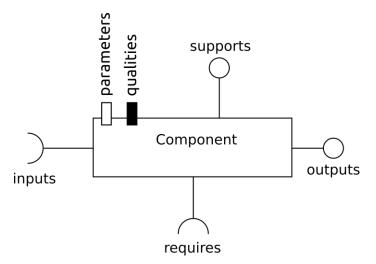

In the black-box view, the component exhibits multiple ports as shown in Figure 6. Every component provides the following six types of ports: *supports*, *requires*, *inputs*, *outputs*, *parameters* and *qualities*.

To graphically distinguish the nature of the ports, we exploit the graphical notation of UML 2 Component Diagrams.

We denote the *supports* port as vertically facing port terminated by a lollipop (circle). The *supports* port is the platform-component part of the composition between a platform and application component. It abstracts the provided resource budget.

The *requires* port is denoted by vertically facing port terminated by a socket (half-circle). The *requires* port is the application-component part of the composition between a platform and application component. The requires ports abstracts the required budget. It serves as an abstraction for settings of configuration parameters and reflecting qualities and costs in the application component.

The *inputs* port is denoted by horizontally facing port terminated by a socket. It represents the intake of data (typically a video stream).

The *outputs* port is denoted by a horizontally facing port terminated by a lollipop. This is a counterpart of the inputs port. It represents the egress of data (typically a video stream).

The *parameters* port exhibits the configuration parameters of the platform component. They are the parameters that can be set to determine the configuration in which the component operates.

The *qualities* port exposes the relevant qualities/costs of the platform component. It determines what aspects of quality and aspects of cost, which may vary across the different configurations, are exposed to be used to express constraints and requirements for quality and resource optimization purposes.

Figure 6 Ports of the components

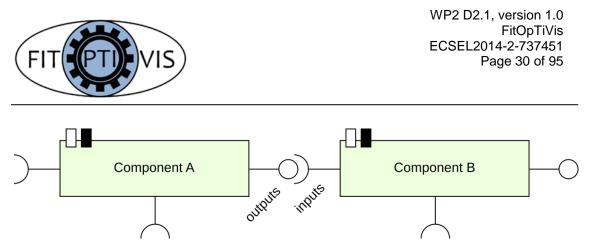

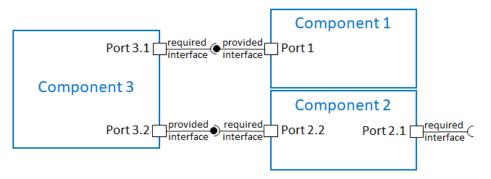

Components can be connected together to form architectures. In this composition, only requires-supports and inputs-outputs connections can be formed, as shown in the figures below.

Figure 7: Horizontal composition by connecting inputs and outputs

Figure 8: Vertical composition by connecting requires and supports ports

The ports further need to be compatible, e.g., video streams have to be of the same encoding, need to be related in terms of frame rate or resolution.

Similarly, when application components and platform components are composed, the budget supported by the platform component should match with the budget required by the application component. This does not necessarily mean that they need to be equal.

Budgets are not necessarily quantitative (scalar numbers) but may include diverse aspects and can be defined at different levels of abstraction.

- A budget may reflect the availability of a feature (e.g., security).

- A budget may include a level of guarantee (e.g., hard real-time vs soft real-time).

- Platform components may enforce budget restrictions on an application component, or monitor if an application stays within its budget.

To reflect this formally in the component model, each port is associated with an interface type. The interface type may define a number of properties that further characterize the contract between two interconnected components. The properties reflect the budgets, quality metrics, resource costs and configurations. The properties may be of different data types – numeric, Boolean, discrete.

When components are connected, a relation is established between properties of components. The connection can be made only between compatible ports. From this

perspective, two ports are compatible if they have compatible interface types and values properties (on the two respective ports) are also compatible. Trivially, if the ports have the same interface type and have the same property values, they are compatible.

#### 4.3.2 White-box view

The white-box view allows modeling the internal structure of a *composite component*. This makes it possible to hierarchically elaborate a component as a composition of other components. The internals of a component are specified as an architecture of interconnected sub-components. This internal architecture follows the same rules as described in the previous section.

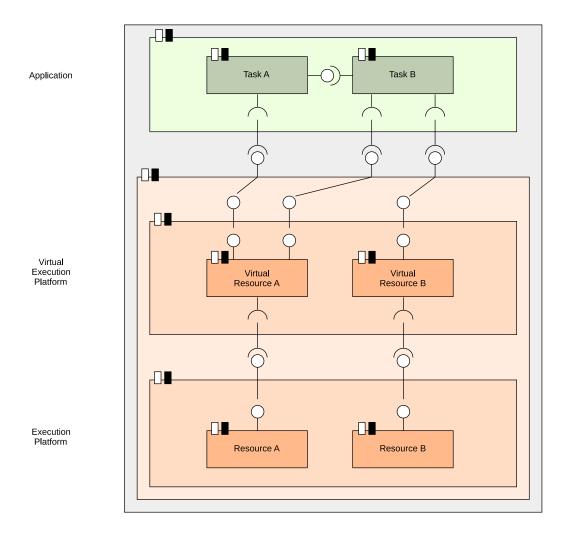

To align the internal architecture with the black-box view, the unconnected ports of the sub-components are delegated to ports on the outer boundary of the composite component. This is depicted in Figure 9, which shows 4 levels of nesting.

On the first level, there is one component that is realized by both hardware and software. Internally, the component is split to an application component and platform component. The application component is internally modeled as two tasks. The platform component internally consists of two layers – the execution platform and the virtual execution platform on top of it. Both the execution platform component and the virtual execution platform component are internally modeled as collections of resources.

The component model thus allows decomposition to an arbitrary level of detail. Generally, the rule of the thumb is to go to such a level of detail that is necessary to model all quality properties, budgets and costs that need to be brought in in the design optimization phase (WP3) and the run-time adaptation (WP4).

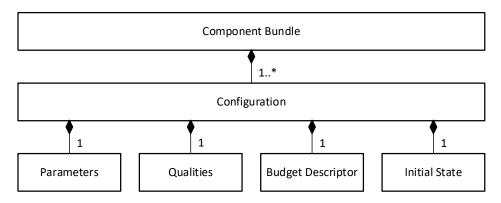

#### 4.3.3 Component configurations

An essential feature of the FitOpTiVis component model is that it explicitly captures the potential design space of component configurations. The component design space in FitOpTiVis is captured by component configurations, internal component properties (to reflect qualities, budgets, costs), and by constraints over the properties.

In particular, a component configuration reflects a discrete variant of the component. The configuration determines the ports (including their cardinality) and mapping of internal component properties to properties of ports. Furthermore, it determines the constraints over the properties. As such, the configuration determines both the black-box and the white-box view of a component.

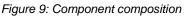

Recalling the example with smart camera – the camera has 6 configurations as given in the table in Section 4.3. In configurations 1-3 it has an outputs port for providing biometric data; in configurations 2-4, it has an outputs port for providing face data; and in configurations 3-6, it has an outputs port for providing video data. In all configurations, the component has an internal property FPS (frames per second). The configuration defines constraints over the FPS property: it is 1 for configurations 1-3, 10 for configurations 4-5, and 30 for configuration 6. The constraints further bind the internal FPS property with the FPS property on the respective output ports.

Figure 10: Smart camera configurations

Additionally, the configuration determines also the required budget / cost consumed. This comprises the energy consumption and GPU allocation, for example.

While in this example, the FPS was fully determined by the configuration, it is also generally possible to see the FPS property as a scale. The configuration then only specifies the permitted range and the dependency between the FPS and cost (e.g., the energy consumption).

This way, the component configurations, properties and constraints together with the component architecture form a design space. Searching the design space for the most fitting configuration and assignment of properties with respect to a cost (e.g., the energy consumption) can be seen as a constrained optimization problem.

#### 4.3.4 Example: Component Abstraction in VR Use Case

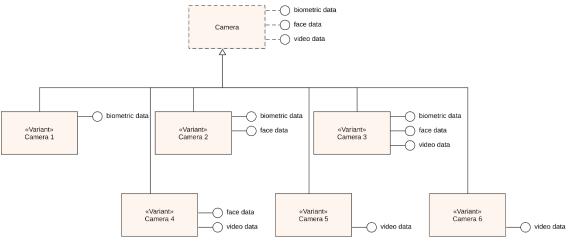

In the context of use case UC-2, Virtual Reality, advanced virtual reality (VR) techniques require high performance computation under stringent latency requirements. Future low latency network services enable the use of remote acceleration of the computation on devices in the edge or the cloud to improve quality of a VR application. We assume in this example that the application and acceleration use OpenCL to define kernels that can be accelerated. Moreover, we assume through portable OpenCL solutions such as POCL [JSS+15] and POCL remote (investigated in FitOpTiVis, WP4) that the application may choose to use a remote OpenCL device for high quality results, or a local device when such a device is not available, or when accessing it would incur too much latency for the application.

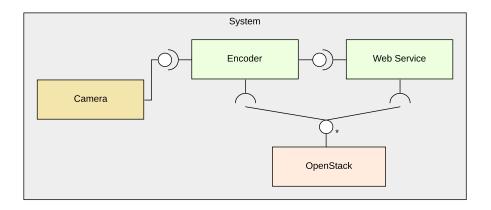

Figure 11: Model of the remote configuration of a stereoscopic VR application

The local device is assumed not to be able to deliver the same quality as the remote device. A (simplistic) model of this system in the component abstraction is given by three platform components, the hand-held device, the network and the cloud accelerator. The network offers communication service between the hand-held device and the accelerator. For the sake of this simple example, the budget provided by the network platform component is a connection, which is characterized by its latency only. The cloud service platform component has OpenCL devices of particular type(s) as its resources and the virtual resource it offers is defined by the number and type of the device.

The application supports two configurations, one corresponding to the local acceleration. It requires no budget from network or cloud service, but only an OpenCL device on the local platform. The application quality includes two aspects, the latency of the application, and the quality of the rendering. We assume that there is a constraint on the latency as stereoscopic VR applications may cause nausea when the latency is too large. The second configuration employs remote acceleration. It requires a network budget to realize a connection to the cloud service. The application latency depends on the network latency. It also requires a budget from the cloud accelerator. In this configuration the application delivers higher quality, but (possibly) at a larger latency.

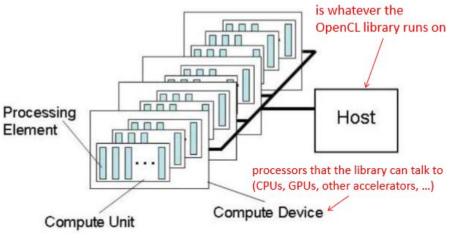

The OpenCL standard includes device types and application models (kernels) but does not include an explicit resource management architecture. (Figure 12 illustrates the concepts and terminology of the OpenCL architecture.) Some of the properties of component may be determined through online monitoring or calibration, such as the latency of the network connection.

© Copyright Khronos Group, 2011

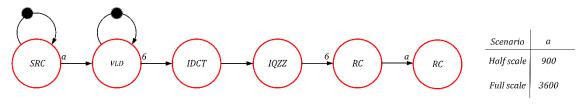

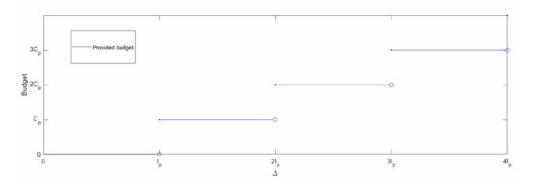

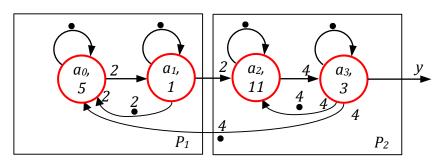

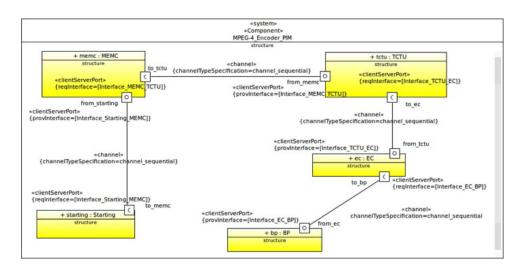

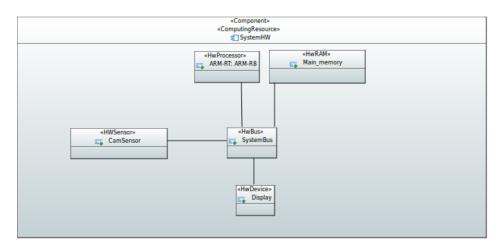

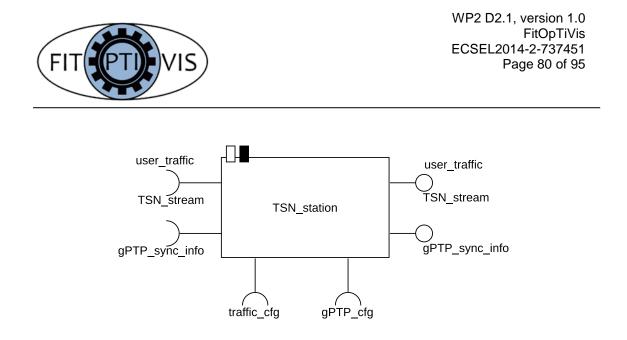

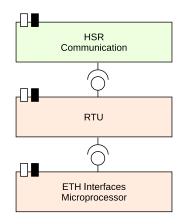

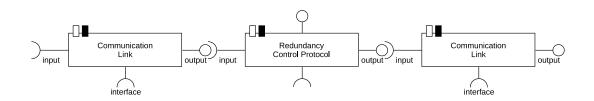

Figure 12: Concepts and terminology in the OpenCL architecture