### ECSEL2017-2-783162

# **FitOptiVis**

From the cloud to the edge - smart IntegraTion and OPtimisation Technologies for highly efficient Image and VIdeo processing Systems

# Deliverable: D4.2 Final run-time models and support for energy, performance and other qualities

Due date of deliverable: 31-05-2020 Actual submission date: 31-05-2020

Start date of Project: 01 June 2018 Duration: 36 months

Responsible WP4: Tampere University (of Technology)

Revision: final version

|                                                                                 | Dissemination level                                                                   |          |  |  |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------|--|--|

| PU                                                                              | Public                                                                                | <b>*</b> |  |  |

| PP Restricted to other programme participants (including the Commission Service |                                                                                       |          |  |  |

| RE                                                                              | Restricted to a group specified by the consortium (including the Commission Services) |          |  |  |

| СО                                                                              | Confidential, only for members of the consortium (excluding the Commission Services)  |          |  |  |

# **DOCUMENT INFO**

Authors (alphabetical order)

| Author                    | Company | E-mail                      |

|---------------------------|---------|-----------------------------|

| Francisco Barranco        | UGR     | fbarranco@ugr.es            |

| Lubomír Bulej             | CUNI    | lubomir.bulej@mff.cuni.cz   |

| Santiago Cáceres          | ITI     | scaceres@iti.es             |

| Tiziana Fanni             | UNICA   | tiziana.fanni@diee.unica.it |

| Dip Goswami               | TUE     | d.goswami@tue.nl            |

| Keijo Haataja             | HURJA   | keijo.haataja@hurja.fi      |

| Pekka Jääskeläinen        | TUT     | pekka.jaaskelainen@tuni.fi  |

| Jiří Kadlec               | UTIA    | kadlec@utia.cas.cz          |

| Francesca Palumbo         | UNISS   | fpalumbo@uniss.it           |

| Jukka Saarinen            | NOKIA   | jukka.saarinen@nokia.com    |

| Raúl Santos de la Cámarra | HIB     | rsantos@hi-iberia.es        |

| Pablo Sánchez             | UC      | sanchez@teisa.unican.es     |

| Carlo Sau                 | UNICA   | carlo.sau@diee.unica.it     |

| Shayan Tabatabaei Nikkhah | TUE     | s.tabatabaei.nikkhah@tue.nl |

| Luis Medina Valdés        | 7SOLS   | luis.medina@sevensols.com   |

Document history

| Version | Date       | Change                  |

|---------|------------|-------------------------|

| V1.0    | 22-05-2020 | Submitted to EU portal. |

### Document data

| Keywords            | runtime platforms, runtime models, runtime adaptation |                                                                                             |

|---------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Editor Address data | Name:                                                 | Lubomír Bulej                                                                               |

|                     | Partner:                                              | CUNI                                                                                        |

|                     | Address:                                              | Faculty of Mathematics and Physics<br>Charles University<br>118 00 Prague<br>Czech Republic |

|                     | Phone:                                                | +420 95155 4189                                                                             |

# **Table of Contents**

| DOCUMENT INFO                                                                            | 2  |

|------------------------------------------------------------------------------------------|----|

| 1. EXECUTIVE SUMMARY                                                                     | 6  |

| 2. DOCUMENT UPDATES                                                                      | 7  |

| 3. INTRODUCTION                                                                          |    |

| 4. RUNTIME PLATFORMS                                                                     | _  |

| 4.1 Managed-Latency Edge-Cloud Environment                                               |    |

| 4.1.1 Probabilistic Latency Guarantees                                                   |    |

| 4.1.2 Probes and Latency Requirements                                                    |    |

| 4.1.3 Platform Status                                                                    |    |

| 4.2 Heterogeneous Distributed Software Runtime                                           | 17 |

| 4.2.1 OpenCL API Extension Candidates                                                    | 18 |

| 4.2.2 Using pocl-remote                                                                  | 20 |

| 4.2.3 Low-Overhead Control Protocol                                                      | 20 |

| 4.2.4 Distributed Event-Based Synchronization                                            | 21 |

| 4.2.5 Platform Status                                                                    | 22 |

| 4.3 Extended OpenMP Runtime Infrastructure                                               | 23 |

| 4.3.1 OpenMP Offloading Requirements                                                     | 23 |

| 4.3.2 OpenMP Offloading Methodology                                                      | 24 |

| 4.3.3 The OpenMP Framework                                                               | 25 |

| 4.3.4 OpenMP and OpenCL Integration                                                      | 25 |

| 4.3.5 Offloading OpenMP threads in a video pipeline                                      |    |

| 4.3.6 OpenMP Extension Status                                                            | 29 |

| 4.4 The CompSOC Platform                                                                 | 31 |

| 4.4.1 Hardware Architecture                                                              |    |

| 4.4.2 Software Architecture                                                              | 32 |

| 4.4.3 Microkernel and RTOS                                                               |    |

| 4.4.4 FitOptiVis QRM Framework on CompSOC                                                | 33 |

| 4.5 The Xilinx Zynq Platform                                                             | 33 |

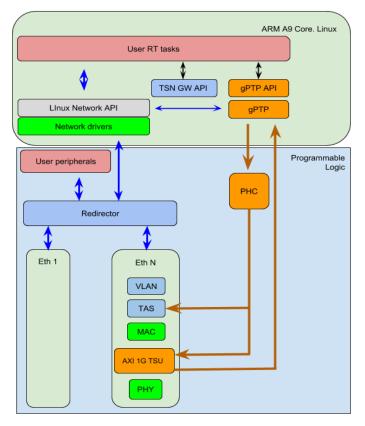

| 4.6 Deterministic Networking Platform                                                    | 33 |

| 4.6.1 TSN bridge design and implementation                                               | 34 |

| 4.6.2 Modelling TSN as a platform component                                              |    |

| 4.6.2.1 Application components:                                                          |    |

| 4.6.2.2 Virtual execution platform                                                       |    |

| 4.6.2.3 Execution platform                                                               |    |

| 4.6.3 Application in Context of UC3 (Habit Tracking)                                     | 39 |

| 4.6.4 Application in Context of UC9 (Surveillance of smart-grid critical infrastructure) | 40 |

| ,                                                                                        |    |

| 5. RUNTIME ADAPTATION                                                       | 42    |

|-----------------------------------------------------------------------------|-------|

| 5.1 Reconfiguration in Managed-Latency Edge-Cloud                           | 42    |

|                                                                             |       |

| 5.1.2 Performance and Interference Models                                   | 46    |

| 5.1.3 Performance Prediction of Co-located Workloads                        | 46    |

| 5.1.4 State of the Art                                                      | 49    |

| 5.2 Reconfiguration on the CompSOC Platform                                 | 51    |

|                                                                             |       |

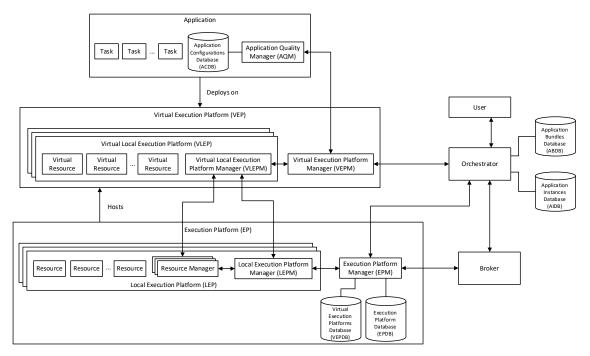

| 5.2.2 Overview                                                              | 52    |

| 5.2.3 Functional Blocks                                                     | 53    |

| 5.2.3.1 Application Quality Manager (AQM)                                   | 53    |

|                                                                             |       |

| 5.2.3.3 Virtual Execution Platform Manager (VEPM)                           | 54    |

| 5.2.3.4 Virtual Local Execution Platform Manager (VLEPM)                    | 54    |

|                                                                             |       |

|                                                                             |       |

|                                                                             |       |

|                                                                             |       |

|                                                                             |       |

|                                                                             |       |

| 5.3 Reconfiguration in Processor/Co-processor Systems                       | 60    |

| 5.3.1 Dynamic Parameter Adjustment                                          | 60    |

|                                                                             |       |

| 5.3.3 Reconfigurable Neural Network Accelerators                            | 63    |

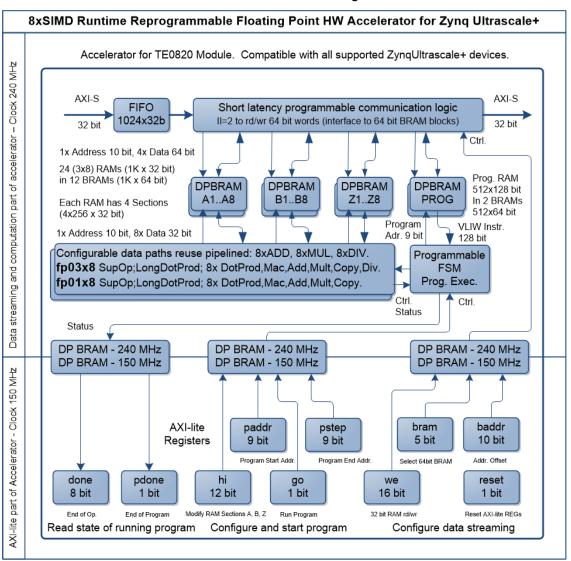

| 5.4 Reconfigurable 8xSIMD Floating-point Accelerators                       | 65    |

| 5.4.1 Design Considerations and Requirements                                | 66    |

| 5.4.2 Reconfiguration by Change of Firmware                                 | 66    |

| 5.4.3 Reconfiguration by Temporary Change of Firmware                       | 67    |

| 5.4.4 Reconfiguration of Streaming Data Path                                | 67    |

| 5.5 Application-Specific Adaptation Scenarios                               | 68    |

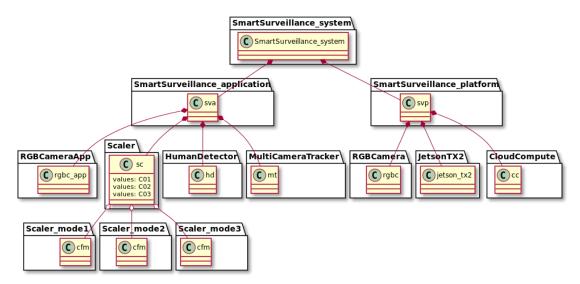

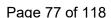

| 5.5.1 Modelling System Variants and Configuration Changes                   | 68    |

| 5.5.2 Selection and Compression of Task-Specific Features                   | 70    |

| 5.5.2.1 Application in context of UC9 (Smart-grid infrastructure surveillan | ce)70 |

| 5.5.2.2 Application in context of UC3 (Habit Tracking)                      | 76    |

| 5.5.3 Distributed Image Pre-Processing and Optimized Image Segmentation     | on81  |

| 5.5.4 Selective On-Demand Resource Loading                                  | 87    |

|                                                                             |       |

| •                                                                           |       |

|                                                                             |       |

| 5.1.1 Edge-Cloud Platform Architecture                                      | 91    |

| A. REVIEW OF VIRTUALIZATION AND RESOURCE MANAGEMEN |     |

|----------------------------------------------------|-----|

| TECHNIQUES                                         |     |

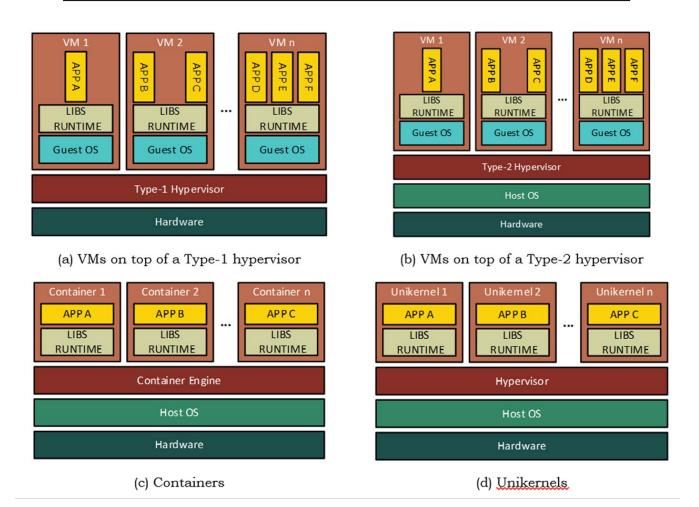

| A.1 State-of-the-art in Virtualization Techniques  |     |

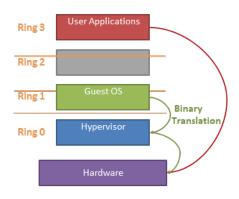

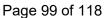

| A.1.1 Hypervisor-based Virtualization              | 96  |

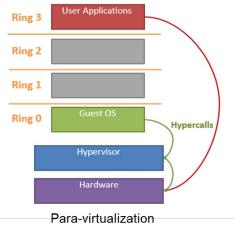

| A.1.2 Container-based Virtualization               | 100 |

| A.1.3 Comparison                                   | 101 |

| A.2 State-of-the-art in Resource Management        |     |

| A.2.1 Resource Types and Models                    | 105 |

| A.2.2 Resource Estimation Models                   | 108 |

| A.2.3 Resource Provisioning Techniques             | 109 |

| A.2.4 Resource Allocation Strategies               | 110 |

| A.2.5 Resource Management Architectures            | 111 |

| A.2.6 Summary and Conclusions                      | 112 |

| A.3 References                                     |     |

Page 6 of 118

# 1. Executive Summary

This report represents deliverable D4.2, one of the outcomes of Task 4.1 in WP4 of the FitOptiVis project. This deliverable is an incremental update of deliverable D4.1. As such, this document retains the content of the previous deliverable and provides new or updated content to reflect the progress made during the second year of the project. The document is intended to be self-contained (and is written from that perspective), so that there is no need to cross-reference the previous version of the deliverable. However, to highlight the differences between D4.2 and D4.1, we provide a dedicated Chapter 2 which lists the new and updated content along with a brief summary.

The main objective of WP4 is to deal with the complexity of application runtime management while considering a diverse set of heterogeneous platform components and configurations. The WP4 solutions provide instances of the WP2 reference architecture described in deliverable D2.1.

This deliverable provides an overview of runtime platforms which represent platform components as defined in deliverable D2.1, spanning levels of abstraction to match the needs of applications with diverse set of requirements. Consequently, our platforms include a latency-managed edge-cloud platform for latency sensitive cloud applications, a distributed OpenCL-centric heterogeneous device runtime software stack which provides a unifying backbone to applications relying on hardware accelerators, both local and remote, an OpenMP runtime built on top of the distributed OpenCL runtime, the CompSOC platform for applications targeting execution on system-on-a-chip, and a deterministic networking platform to support time-sensitive applications with mixed-criticality communication requirements.

To enable adaptive control of application quality attributes (e.g., image resolution and quality, or frame rate) in response to resource availability and the desired quality trade-off, the runtime platforms need to provide means for resource managers to control application parameters linked to individual quality attributes and to manage resources assigned to an application. Each of the platforms enables adaptation at different levels of abstraction and at different time scales. To facilitate design of the necessary management interfaces, the deliverable also reports on adaptation scenarios relevant to use cases from various partners contributing to WP4.

The content of this deliverable contributes to milestones MS5 (M18 specification update) and MS6 (M24 partial demonstrators).

# 2. Document Updates

This chapter provides a brief summary of specific content that has been updated or added to D4.2 with respect to D4.1. Naturally, Chapters 3 and 6 have been updated to reflect the new content.

#### 4.1 Managed-Latency Edge-Cloud Environment

Updated platform status in Section 4.1.3 to include information about the newly developed performance predictor (further elaborated in Section 5.1.3).

### 4.2 Heterogeneous Distributed Software Runtime

- Added description of the low overhead control protocol and the distributed eventbased synchronization which has been implemented in the runtime.

- Updated the status of the internal release of pocl-remote.

#### 4.3 Extended OpenMP Runtime Infrastructure

- Updated Section 4.3 to reflect new OpenMP offloading requirements.

- Added Section 4.3.2 describing the development of a new approach for code offloading based on an LLVM pre-processor pass and integration of the offloading methodology in an open source compiler (clang).

- Added Section 4.3.5 providing an analysis of the use of OpenMP for offloading threads in a video pipeline.

#### 4.5 The Xilinx Zyng Platform

Removed Section 4.5.1 (Inter-Cloud Connectivity with Arrowhead) as obsolete.

#### 4.6 Deterministic Networking Platform

- Updated description of a TSN bridge design and implementation to reflect usecase requirements in Section 4.6.1.

- Added Section 4.6.2 with a QRML model of TSN as a platform component, with details concerning configuration parameters of individual components and runtime monitoring provided by the time synchronization component.

- Added Sections 4.6.3 and 4.6.4 describing application of TSN in different use cases.

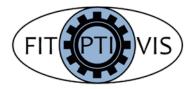

#### 5.1 Reconfiguration in Managed-Latency Edge-Cloud

Added Section 5.1.3 with an overview of a performance predictor which uses a

novel technique for statistical prediction of the upper bound of the response time

of a service sharing the same computer with other services.

#### 5.2 Reconfiguration on the CompSOC Platform

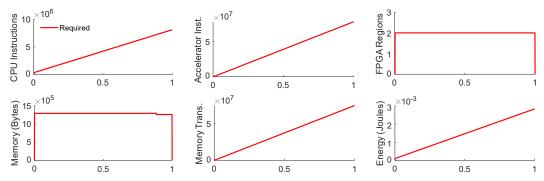

Added Section 5.2.4 describing an analytical framework for budget matching, which allows to determine if the provided budget matches the required budget in presence of multiple resources of different types. The framework is an important ingredient of quality and resource management support in FitOptiVis.

#### 5.3 Reconfiguration in Processor/Co-processor Systems

- Updated Section 5.3 to describe integration of an overlay monitoring layer in the processor-coprocessor system, which enables collection of runtime metrics and subsequently runtime estimation of selected performance indicators.

- Added Section 5.3.3 describing initial definition and evaluation of a coprocessor for the Water Supply use case, which will be used to assess the envisioned dynamic parameter adjustment strategy.

#### 5.4 Reconfigurable 8xSIMD Floating-point Accelerators

• Introduced support for reconfigurable floating-point accelerators on the Xilinx Zynq platform. Individual subsections provide description of the accelerator architecture, design considerations, and supported reconfiguration scenarios.

#### 5.5.1 Modelling System Variants and Configuration Changes

• Updated the description of the modelling approach to take advantage of QRML, the FitOpTiVis DSL for capturing quality and resource management models.

### 5.5.2 Selection and Compression of Task-Specific Features

- Updated strategies for bandwidth reduction using regions of interest and described the application of the bandwidth reduction strategies in the Habit Tracking (UC3) and Smart Grid (UC9) use cases.

- Added QRML models of system components, along with component descriptions and reconfiguration scenarios in UC3 and UC9.

#### 5.5.3 Distributed Image Pre-Processing and Optimized Image Segmentation

Added QRML model of the Edge component, along with description of the relevant monitored metrics and reconfiguration scenarios to enable runtime adaptation to achieve the desired performance.

### 3. Introduction

Work package 4 addresses Objective 3 of the FitOptiVis project:

**Objective 3**: Real-time multi-objective combinatorial optimisation; data and process distribution; run-time adaptation through virtualization; run-time quality and resource management; energy driven adaptations; workload (re-)distribution; support for run-time upgrades.

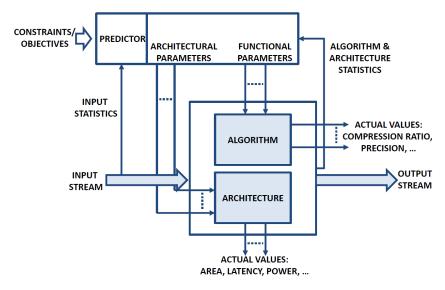

Specifically, in WP4 the consortium develops techniques for run-time resource management within the system architecture template outlined in WP2. The main goal is to deal with the complexity of application runtime management, reconfiguration, and monitoring, while considering a diverse set of heterogeneous platform components and configurations. To increase developer productivity and to promote vendor independence with respect to compute platform, this diversity should become transparent from an application developer's point of view. Task 4.1 focuses on run-time technologies and models to support management of performance, energy, and other qualities. This deliverable reports on the outcomes of the first two years of the project.

In Chapter 4, the report provides an overview of technologies that provide basis for virtual reconfigurable platforms and concrete platform components as defined in the FitOptiVis reference architecture (see deliverable D2.1). To satisfy the diverse set of requirements found in FitOptiVis use cases, multiple concrete platforms are needed, each tailored to serve different types of requirements. For example, while real-time applications with modest latency requirements and a time frame for reconfiguration measured in seconds may be well served by a solution utilizing a general-purpose compute cluster in an edge-cloud environment, a hard real-time application implementing a tight control loop may need to utilize custom FPGA accelerators to meet its latency requirements. Building a single unified hardware, software, and tooling framework to satisfy vastly different requirements would be neither possible, nor desirable. Instead, in FitOptiVis, we aim to unify at the level of concepts, principles, and abstractions to identify and extract commonalities found in different domains.

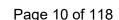

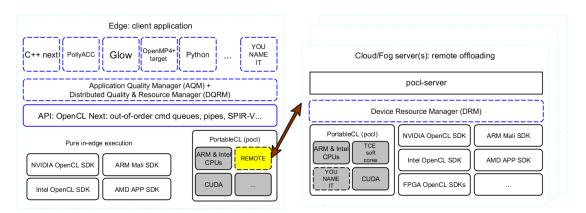

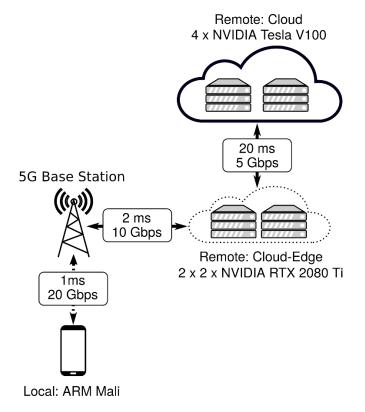

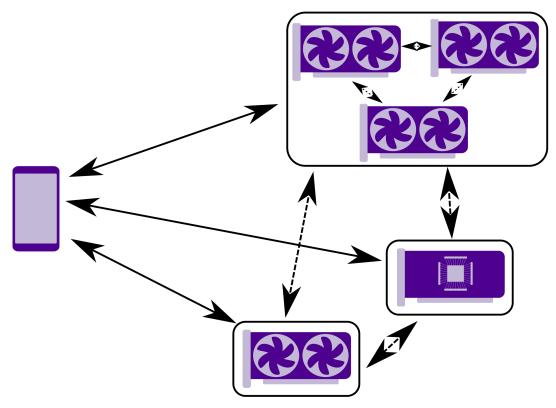

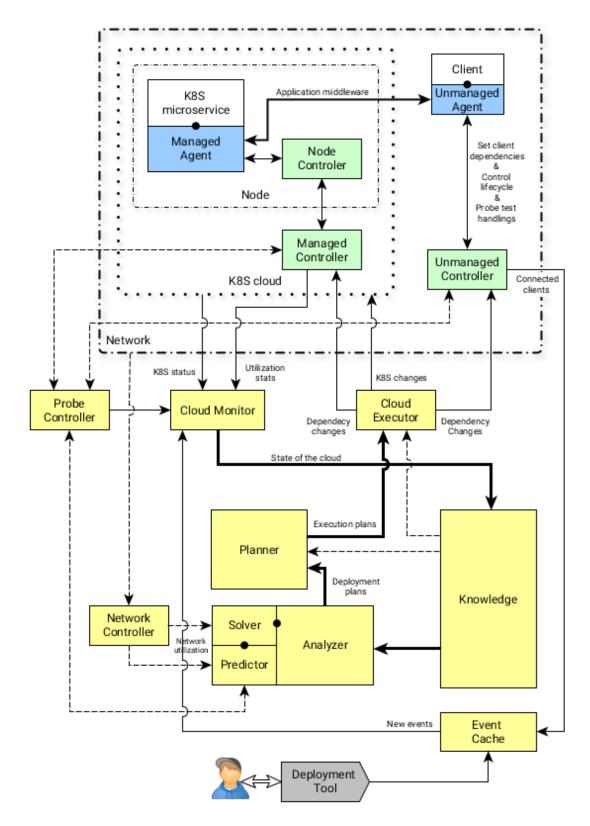

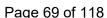

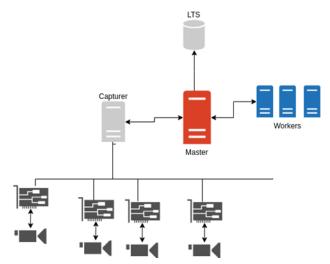

The idea is that the technologies developed in WP4 each serve a particular purpose and are intended to be used as building blocks for implementing different use-cases and demonstrators. This is captured in Figure 1, which shows an example instantiation of the runtime technologies in a "Multi-access Edge Computing" setup, which is a computing model comprising a local edge device (a lightweight terminal computer such as a smart phone or a smart camera) connected to a nearby edge-cloud (or a cluster of GPU and/or FPGA accelerator servers) using a fast network connection. In the context of FitOptiVis, use-cases such as UC2 and UC3 are examples of such a computing model.

Figure 1. An example instantiation of WP4 technologies in a Multi-access Edge Computing (MEC) scenario (which applies to several use cases in the project), with different tools serving specific purposes in the implementation of the system. OpenMP serves as a layer which boosts developer productivity in defining the Terminal/Edge application. Pocl-remote is used for distributed computing across diverse heterogeneous resources. MECE handles the server-side control loop, taking into account the latencies incurred both by the potential virtualization of the server-side resources as well as the application running on the edge device. If required by an application, CompSOC can be used for managing hard real time guarantees at a Systemon-a-Chip level. Different reconfiguration mechanisms (with different granularity) can be used to program FPGA devices on the fly—based on the requirements of the application being accelerated. MDC provides reconfiguration at task granularity, presenting a CGRA overlay architecture that can be implemented either as a FPGA soft core, or as an ASIC in a new SoC, FP SIMD FPGA overlays add runtime reconfigurable floating point accelerators, whereas AIPHS can generate monitoring (bus snooping) hardware to be utilized in the FPGA-based accelerators, which is discussed more thoroughly in D4.3. Finally, TSN can be used to synchronize the times of multiple server nodes to provide meaningful timestamps and accurate time triggered events as well as provide support mixed-criticality network traffic on shared network infrastructure. FIVIS enables global (system-of-systems level) profiling and performance data analysis.

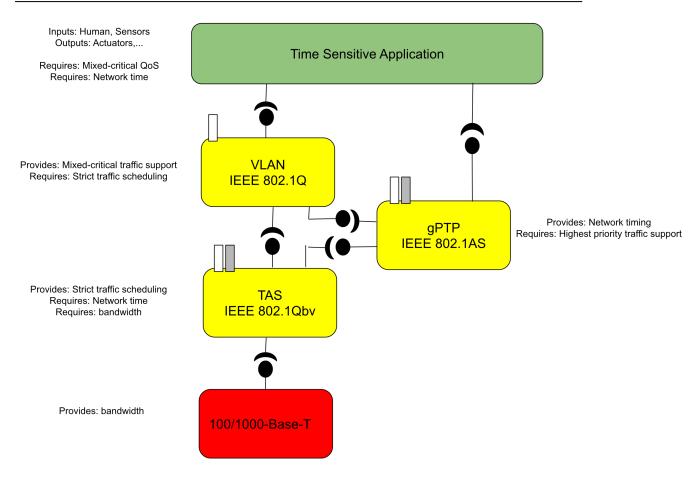

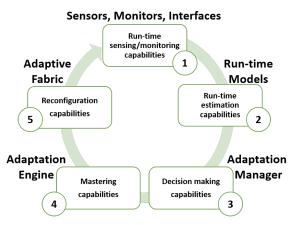

A common theme of FitOptiVis systems is adaptive runtime management of various quality aspects through adjustment of configurable system parameters. The architecture of adaptive systems is often based on the MAPE-k loop [KEP03] architectural pattern, which provides a general concept of a control loop. Systems implementing such control loops can be nested to form a hierarchy of control loops operating at different time scales. This approach can be also applied in FitOptiVis, where a top-level MAPE-k loop can operate at the time frame of seconds, determining the setpoints for a lower-level control loop operating at the time scale of milliseconds or even microseconds. The presented technologies are intended for solutions operating at different time scales.

Section 4.1 describes a *multi-node managed-latency* private *edge-cloud* platform that will provide probabilistic guarantees to parts of applications (time-sensitive services) with *soft real-time* requirements which will be deployed in the edge-cloud. The platform aims to support solutions with reconfiguration time frames in seconds, which can be either general soft real-time services, or top-level adaptation control loops managing set points for lower-level control loops. By focusing on probabilistic guarantees, we aim to reduce the impact on developers by not requiring them to express application performance

Page 11 of 118

requirements through many low-level metrics, but rather through a simple end-to-end metric defined on probe points provided by an application.

For interactive applications targeting shorter time frames, Section 4.2 provides a description of a distributed, heterogeneous-device runtime software stack based on OpenCL, which can be used to spread the execution of application's computational tasks to all available resources (local or remote), and which can be fully controlled from the application running on a terminal device. The foundation for an extensible and portable heterogeneous system-software stack had been laid out in the ALMARVI project, and is being extended in FitOptiVis to support new use cases in distributed and reconfigurable computing. This part directly addresses the objective of managing the complexity of a heterogeneous distributed execution platform and allowing an application to harness all available resources through a standardized API. Because OpenCL can encapsulate all types of compute devices ranging from general-purpose CPUs to fixed-function accelerators, the consortium believes that the diversity management goal is well met by relying on it as a backbone, by enabling easy support/integration path for the various hardware-software platforms developed in the project by partners, and by extending the standard whenever needed. Section 4.2 also lists potential extensions to the OpenCL API that will enable runtime monitoring, among other requirements associated with a distributed, dynamically changing environment. OpenCL supports heterogeneous task graphs via its command queue abstraction, which provides a basis for distributed heterogeneous task scheduling, which also helps Task 3.2 (Programming and Parallelization Support).

A higher-level programming model, OpenMP 5, is being added as an example of an enduser programming language on top of the developed stack. This addresses the goal of *transparency*. Because the OpenMP view of the platform components is more restricted than that of OpenCL, more decisions on the suitable devices for each function are delegated to the management layers in the stack, instead of relying solely on the programmer. The OpenMP 5 offloading support developed on top of the OpenCL based stack is described in Section 4.3.

For the lowest-level solutions operating at the shortest time frames, Sections 4.4 and 4.5 discuss two hardware-software platforms that are being supported and extended in the project: the CompSOC platform for composable and analysable hard real-time applications running on a single system-on-a-chip, and platform templates tailored to Xilinx Zynq-based FPGA SOCs as an easy-to-use implementation and prototyping platform. Both platforms target and support high-performance embedded computations, but place themselves in different layers of the work done within FitOptiVis: CompSOC defines a complete framework for design and implementation of hard real-time applications which utilize resource sharing, while the presented FPGA platforms enable prototyping and integrating of any hardware platforms with ease. The presented Xilinx-based platforms make a connection to the design flows in WP3 (Design-time support) allowing to prototype and utilize new hardware IP in combination with already commercialized ones running in the same system as described in WP5 (Devices and components).

An important component of any distributed system is the communication fabric. In the context of edge-cloud, we are mostly dealing with common networking technologies. However, many of the use cases are built around time-sensitive applications which need to exchange data with different levels of criticality. Section 4.6 therefore introduces a

Page 12 of 118

platform component providing deterministic networking, which caters to the needs of time-sensitive applications. To this end, the platform provides a custom time-sensitive networking bridge built on top of standard networking technologies.

Chapter 5 deals with support for adaptation in the runtime platforms and applications built on those platforms. To support different trade-offs between various quality aspects (visual quality, resolution, latency) and resource usage (compute resources, I/O bandwidth, memory consumption), the architectural description of FitOptiVis applications (see Deliverable D2.1) will enable binding individual quality aspects to corresponding resource requirements. It will also expose configurable parameters that allows a runtime entity, e.g., an adaptation manager, to request a particular quality level for a specific aspect. Such an adaptation manager will then control the individual parameters to achieve a higher-level goal, e.g., best overall quality given fixed amount of resources, minimal resource usage, best quality possible, etc. The adaptation manager needs to closely co-operate (or be integrated) with the platform runtime in order to ensure that the resource requirements associated with the desired levels of different quality aspects are satisfied.

Similarly to Chapter 4, we have to deal with adaptation at different levels of abstraction corresponding to the supported runtime platforms. In Section 5.1 we, therefore, provide an overview of adaptation support in the context of the managed-latency edge-cloud platform, where the system needs to manage deployment of applications to individual nodes as well as allocation of resources such as CPU time, memory, and I/O bandwidth to co-located applications. For applications targeting systems-on-a-chip implementation and shorter time frames, Section 5.2 presents an overview of adaptation mechanisms and management interfaces on the CompSOC platform, along with mapping of CompSOC concepts to the FitOptiVis reference architecture and a mechanism to match provided and required budgets. Section 5.3 provides an overview of adaptation support for reconfigurable hardware, specifically targeting reconfigurable neural network accelerators, and Section 5.4 presents reconfigurable SIMD floating-point accelerators. Section 5.5 collects application-specific adaptation scenarios related to use cases from partners contributing to WP4, elaborating on the supported system configurations, conditions which trigger reconfiguration, monitored parameters, and other scenariospecific requirements.

Chapter 6 provides a short conclusion, briefly summarizing the advances during the first two years of the project.

In addition to the main document, the deliverable also contains a survey of existing virtualization and resource management techniques, which provides a basis for new contributions in FitOptiVis. The survey is included in Appendix A.

Page 13 of 118

Page 14 of 118

### 4. Runtime Platforms

This chapter provides an overview of technologies and concrete platforms that will serve as a basis for virtual reconfigurable platforms as defined in the FitOptiVis reference architecture. We describe the platform model and the correspondence to architectural concepts defined in WP2 (Reference architecture, virtual platform and integration), i.e., the "instantiation" of the WP2 architecture on a specific platform. Each platform serves to satisfy a different subset of the diverse requirements present in FitOptiVis use cases and is intended to applications operating at different time frames.

# 4.1 Managed-Latency Edge-Cloud Environment

Modern Cyber-physical Systems (CPS) rely on data from sensors and perform computationally-intensive tasks on the data (computer vision, data analytics, optimization, and decision making, learning and predictions) which often cannot be executed on edge devices due to the limited energy budget and computational power.

To obtain the necessary computational power, such systems are typically split into parts that execute on edge devices and parts that execute in the cloud. However, the connection with the physical world inherent to CPS requires these systems to operate and respond in real-time, whereas the cloud was primarily built to provide average throughput through massive scaling. The real-time requirements impose bounds on response time, and when executing tasks in the cloud, a significant part of the end-to-end response time is due to communication latency.

The concept of edge-cloud aims to tackle this problem by moving computation to computational clusters that are physically closer to edge devices. While this reduces communication latencies, edge-cloud alone does not guarantee bounded end-to-end response time, which becomes more dominated by the computation time. The reason is that while the cloud itself focuses on optimizing the average performance and the cost of computation, it does not provide any guarantees on the upper bound of the computation time of individual requests. To satisfy the needs of modern cloud-connected CPS we need an approach that can reflect the real-time requirements of modern CPSs even with cloud in the computation loop.

# 4.1.1 Probabilistic Latency Guarantees

Strict latency guarantees on each individual request are the domain of real-time programming, which comes at a very high price, as it forces developers to use a low-level programming language, severely limits the choice of libraries, and imposes a relatively exotic programming model of periodic non-blocking real-time tasks.

We instead advocate the use of standard cloud technologies (i.e., micro-services running in a container-based cloud such as Kubernetes) and modern high-level programming languages (e.g., Java, Scala, Python). However, we restrict ourselves to a class of applications for which soft real-time guarantees are enough (i.e., the guarantee on the end-to-end response is probabilistic, such as "in 99% of cases the response comes in 100ms and in 95% of cases the response comes in 40ms").

It turns out that this is acceptable to a wide class of applications including augmented reality, real-time planning and coordination, video and audio processing, etc. Generally speaking, this class comprises any application that has a safe state and has a local

Page 15 of 118

control loop that keeps the application in the safe state while computation is done in the cloud. Consequently, the soft real-time guarantee pertains to qualities such as availability and optimality, but not to safety. In the context of the FitOptiVis project, which generally focuses on developing distributed image and video processing pipelines, this applies to many of the use cases (augmented reality, habit tracking, municipal speed cameras, etc.).

## 4.1.2 Probes and Latency Requirements

One of the goals of our work is to minimize the impact of using a managed-latency edgecloud environment on application developers. Given that we aim to use standard cloud technologies, we also envision the developer creating artefacts, e.g., for the Kubernetes (K8S) platform. The only required extension is the specification of application real-time requirements in the application deployment descriptor.

Contrary to common cloud deployment practices, we aim to spare the developer from dealing with the selection of VM type, the number of virtual CPUs, memory, IOPS, etc. Similarly, we aim to avoid specification of auto-scaling rules (including triggers), because we consider these to be implementation details of the cloud platform's internal mechanisms which the developer is not equipped to set correctly without an experiment.

We instead work with an abstraction in which the developer is responsible for providing the application and its soft real-time requirements, while the responsibility for assessing the performance of the cloud application, as well as allocating resources (i.e., the required number of virtual CPUs, memory, IOPS, etc.) and making scheduling and deployment decisions so as to ensure that the (probabilistic) guarantees are met, lies with the cloud platform. Consequently, if the platform determines that it cannot satisfy the requirements, it will not admit the application for deployment.

Specifically, when developing an edge-cloud application, the developer has to describe the application in terms of an auto-scaling micro-service with added communication latency requirements. In the specific case of the Kubernetes cloud platform, we extend the Kubernetes application deployment descriptor to allow declaration of measurement *probes*, special functions provided by the developer which the system uses to assess the performance of the application in a particular deployment scenario.

An example deployment descriptor for a sample face-recognition application is shown in Listing 1. The timing requirements for the application state that the response of the application on the "recognize" probe should be below 100 milliseconds in 99% cases, and below 50 milliseconds in 95% cases.

```

kind: Deployment

metadata:

name: recognizer-deployment

labels:

app: recognizer

spec: # microservice specification

template:

metadata:

labels:

app: recognizer

containers:

- name: recog

image: repo/recog

ports:

- containerPort: 7777

probes: # probes

- name: recognize

timingRequirements:

- name: recognize limit

probe: recognize

limits:

- probability: 0.99

time: 100 # Max. 100ms in 99% cases

- probability: 0.95

time: 50 # Max. 50ms in 95% cases

```

Listing 1. Application deployment descriptor with timing requirements

A probe (or a set of probes) has to capture the essential behaviour of the application so that when invoked by the cloud-edge platform, it will provide a representative sample of the application's performance in the current deployment configuration. Expressing the application timing requirements over developer-supplied probes simplifies the specification of the contract between the application and the cloud-edge platform, and allows it to treat the application as a black-box.

#### 4.1.3 Platform Status

The development of the managed-latency edge-cloud platform is in progress. During the first year of the project, several design iterations have been made and work on prototype implementation has been started. Inter-module interfaces, application middleware, and module prototypes have been implemented.

During the second year of the project, in addition to continued platform development, we have been investigating methods for performance prediction of co-located workloads. Specifically, we focused on developing a prediction method that uses of performance measurements collected while executing different combinations of co-located workloads to predict performance of new, previously unseen, workload combinations. In addition, we have been working on experimental methods to automatically establish the operational boundaries of the predictor.

Given the experimental nature and possibly involved installation and configuration of the prototype, we plan to make the platform available as a hosted service during the third year of the project. We will work closely with partners interested in deploying parts of their application in a managed-latency edge-cloud environment.

### 4.2 Heterogeneous Distributed Software Runtime

The development of a single-node heterogeneous software stack based on OpenCL was initiated in the ALMARVI project. In FitOptiVis, this stack is being extended to support a distributed edge-cloud setup that can map the architecture models defined in WP2 to concrete run-time concepts of execution platforms and their topologies while supporting new devices developed with WP3 technologies and other devices and components of WP5.

The primary questions we seek answers in the runtime stack development for are:

- What are the workloads that need to be executed on local devices given 5G, WiFi6 and other high-speed low-latency wireless network technologies?

- Where are the latency bottlenecks when offloading interactive applications across such networks to cloud-edge servers?

- Can we distribute event synchronization to minimize communication due to back-and-forth synchronization between the "application device" and the cloudedge servers?

These questions are approached by developing a proof-of-concept heterogeneous runtime that is optimized also for low-latency tasks and which can support also other types of computation offloading in addition to those based on frame serving (e.g. cloud gaming which has become popular in the recent years).

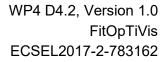

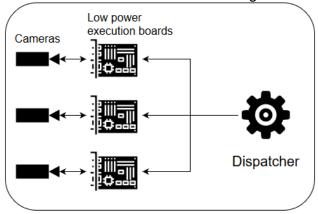

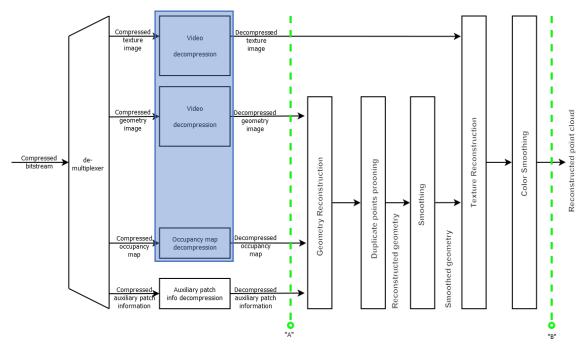

The software stack being developed is shown in Figure 1, while an example usage context is shown in Figure 2.

Figure 2. Multi-node heterogeneous distributed software runtime stack.

Figure 3. An example use context for the distributed runtime software stack. A terminal device (here a smartphone) deploys and starts the OpenCL application which then through a fast wireless link communicates to remote GPU devices in clusters at the cloud-edge and in the cloud.

# 4.2.1 OpenCL API Extension Candidates

The current notion is that OpenCL can serve as a good basis for a compute API both in local and distributed scenarios. However, already during the first year of the project, we identified the following features, which might be beneficial to add to the API (first as extensions and later as official part of the standard) to better support remote cloud-edge offloading scenarios:

- Platform: **Device Proximity**. The existing OpenCL API (practically) does not model connectivity between devices. Devices are assumed to reside in a single computer and to be accessible at most via a system bus such as PCIe or AXI, with shared external memory and/or per-device external memory. It would be beneficial to allow applications to make offloading decisions based on how efficiently devices are connected together: the API could be a platform-level query API with a possibility to query for the link between two devices. How the links are modelled and categorized is an open question at this point. E.g. 1) same shared-memory hierarchy, 2) same system bus, 3) in the same local network, 4) internet connectivity

- Device: **Link Status**. Especially with 3) of the previous item and especially with 4), the performance of the link heavily depends on the simultaneous traffic and other varying conditions (e.g. the proximity of the nearest 5G base station). It would be useful to be able to monitor historical statistical information of the link's

Page 19 of 118

performance (e.g, in the past 5 seconds, or the past 5 buffer transfers). Because it is hard to isolate the network part's time from the client side code, it might be useful as an OpenCL runtime API. Of course the most important link status information is whether the link is working in the first place, as it affects the reachability of the device.

- Device: Reachability. In OpenCL there is already a flag for 'availability' of the device. This might be reused for scenarios where a remote device is temporarily unavailable due to networking issues.

- Command Queues: Performance History. Auto-tuning scenarios attempt to execute a kernel on multiple devices while varying parameters that affect execution. While the information is natural to reside on the client side of the OpenCL API, it might be useful to provide some level of support in the runtime API for querying the estimated performance of the given kernel. The kernel performance estimate might be identified with a hash and input buffer sizes or similar. It might be difficult to design this API to fit OpenCL therefore it might be better to keep it in a client-side helper API layer.

- Command Queues: Command's Energy Consumption. Now the profiling command queues allow storing time stamps of events. In terms of tuning the power performance, it might be interesting to also record the consumed energy in case the target supports such information. This might be difficult to get accurate as it's hard to account for which kernel consumed the energy in the processor especially if there are multiple ones running. It's worth researching at least for the dedicated GPU farm scenario where we execute one kernel at a time and might then resort to average power numbers which can be multiplied with the execution time. The OpenCL API could be connected to the profiling command queues time stamping system: the time stamps could also record "energy stamps" at a similar incremental fashion.

- Command Queues: More Profiling/Performance Counters: Advanced profiling

information could include the cache hit miss counter values in a similar stamping

fashion with the same caveat as above: in case multiple kernels are executing

at the same time, it might be difficult to isolate which kernel caused which part of

the cache level misses.

- Device: **Temperature Readings** of the processor/memories or any other components equipped with a temperature sensor.

- Command Queues: Real Time Commands with Execution Cancellation: In some soft real time cases we can just reduce quality when a kernel takes too long time. It would be useful to provide mechanism to the command queues that allow killing a kernel when a time limit is reached. This could yield a special "timeout event" which other commands could listen to and kill also the next ones that are dependent on the regular finish event that the killed command should have produced.

- Buffers: Unreliable Buffers: This is connected to the soft real-time case and the

cancelled kernels, and not delivering full data in time, but still producing some

useful data. E.g. when we produce images in a tiled fashion, it may be useful to

display a partially rendered/decompressed frame, especially when applying

heavy filtering on top of it or when it's assumed that the incomplete frame in

general looks OK if there are enough complete frames displayed per second.

• Buffers: **File-initialized Buffers**: Some of the buffer content could be initialized from files (possibly an URI) in the system where the remote Device resides. This is currently not possible in OpenCL as it only allows initialization from an array.

### 4.2.2 Using pocl-remote

To provide the reader with an idea on how remote offloading works with pocl-remote, brief usage instructions are given here, while a more detailed documentation, including build instructions, can be found at:

https://github.com/cpc/pocl-fitoptivis/blob/master/doc/sphinx/source/remote.rst

On the server, the clinfo command must list at least one OpenCL device. The server can be then started using the following command:

```

./server/pocld <IP ADDRESS> <PORT>

```

Note that pocld will listen on two ports, PORT and PORT+1. The number of messages produced by the server can be adjusted by setting the POCLD\_LOGLEVEL environment variable to the desired level before running pocld. The default log level is err. The server accepts the following log levels: debug, info, warn, err, critical, and off. On the client, the following environment variables need to be exported:

```

export POCL_DEVICES=remote

export POCL_REMOTEO_PARAMETERS=<IP ADDRESS>:<PORT>/<DEVICE ID>

```

The IP ADDRESS and PORT values are self-explanatory. PORT is the lower of the two port numbers assigned to the server. The DEVICE ID is the index of the device on the server. Valid indices range from 0 to N-1, where N is the total number of devices across all platforms on the server. The index is the order in which pocld lists the devices in the OpenCL platform it uses. This is the same order as displayed by clinfo.

The clinfo tool can be used to perform a "smoke test" to ensure that the distributed setup works. When configured properly, the tool should also list remote devices:

```

$ clinfo|grep pocl-remote

Device Version OpenCL 1.2 CUDA HSTR: pocl-remote 123.456.789.123:10998/0

```

A simple dot-product example can be then run by executing the example binary:

```

$ cd examples/example1

$ ./example1

(0.000000, 0.000000, 0.000000, 0.000000) . (0.000000, 0.000000, 0.000000, 0.000000) = 0.000000

(1.000000, 1.000000, 1.000000, 1.000000) . (1.000000, 1.000000, 1.000000, 1.000000) = 4.000000

(2.000000, 2.000000, 2.000000, 2.000000) . (2.000000, 2.000000, 2.000000, 2.000000) = 16.000000

(3.000000, 3.000000, 3.000000, 3.000000) . (3.000000, 3.000000, 3.000000) = 36.000000

OK

```

#### 4.2.3 Low-Overhead Control Protocol

Use of a more general and feature-rich communication framework was foregone in favour of working directly with TCP sockets that have been configured for minimum possible OS-side latency, and packets with well-defined in-memory representation to remove any serialization and deserialization overhead associated with more general purpose portable data representations.

The protocol is implemented as plain C structures whose in-memory representation is fixed and which start with a field signifying their exact type, i.e. using the tagged union pattern. The downside of this approach is that all variants end up being padded to the size of the largest existing variant. Initial testing has shown that this introduces as much

Page 21 of 118

as a couple of kilobytes in overhead, as most packets are less than a few hundred bytes. This includes buffer transfers, as the machine-learning frameworks we tested initially ended up creating dozens (up to hundreds) of less than kilobyte-sized buffers.

To address this, command-specific size value is sent before the structure and the part of the structure that goes over this size is left undefined since it will not be accessed when handling the given command. This adds slight overhead due to requiring an extra read call to the network driver, but still avoids a more traditional deserialization step.

### 4.2.4 Distributed Event-Based Synchronization

Inter-command synchronization is handled internally on the remote servers by utilizing event dependency information as well as buffer dependencies extracted from in-order queues. This way commands can be started as soon as they are received, given their dependencies are met and the execution can proceed independently from the host device, avoiding round-trips to the main device, which can heavily impact the perceived overall latency.

Results are sent back to the host from a separate thread that polls in-flight tasks in order to send the reply as early as possible without interrupting reception of new tasks nor execution of the current ones.

Tasks spread across multiple devices are synchronized on two levels: between devices on the remote server no extra network communication to the application is needed beyond notifying the host application of task completion, as illustrated in Figure 3. For synchronization between different remote servers, an extra thread is added for every peer to listen for incoming data migration requests. This way the host application does not need to be involved after firing off the initial migration command, and the command only needs to be dispatched to one remote server. Remote servers are assumed to be located in close proximity to each other (in the same data center), and thus to have much faster connections to each other than to the host application.

Figure 4. Multiple levels of data transfer and event signalling - application to remote server, peer-to-peer communication between servers and direct transfers between devices in a single server

#### 4.2.5 Platform Status

The distributed OpenCL runtime is being implemented within the Portable Computing Language (POCL) open source project, with internal releases made available to the project partners until the runtime becomes mature enough for general use by the open source community, at which point the code will be published at http://code.portablecl.org.

At the time of writing this document, the latest internal release available to project partners at https://github.com/cpc/pocl-fitoptivis was labelled as version 0.7 with the following feature highlights:

- Remote code includes work to make event processing more asynchronous

- ALMAIF driver was updated and optimized; some new features (see docs for details):

- Hybrid compilation (allows running tests on TCE and then same tests on FPGA via ALMAIF, without having to change test code to load from binaries)

- Linux UIO support (possible to run programs without root)

- TCE was made thread-safe, new driver call-backs implemented, new math library functions implemented

- Glow tests added, TCE driver should now pass 90%+ of tests

- Improved support for more complicated multiple-device setups

- Android support

Page 23 of 118

We now consider the runtime to be in "optimization stage", because the main known stability issues have been resolved. The rest of the time in FitOptiVis will be spent on further scalability and performance improvements.

# 4.3 Extended OpenMP Runtime Infrastructure

OpenMP is the de-facto standard for parallel programming of Symmetric Multi-Processing (SMP) architectures with shared memory. During the last years, OpenMP specifications have been adding new features to support parallel programming on heterogeneous platforms. In fact, recent releases of popular compilers (such as gcc and clang) support the latest OpenMP specification (5.0), which supports runtime offloading of code to different devices such as NVIDIA GPUs, Intel Xeon-Phi co-processor, and multi-core architectures.

The OpenMP target offloading methodology differs from approaches used in other parallel programming environments such as OpenCL. In OpenMP, the code to be offloaded is precompiled for all targeted devices at build time. This main disadvantage of this approach is that all target devices must be supported by the OpenMP compiler. In contrast, OpenCL relies on compilation at runtime, which makes it easy to support new devices as they become available, but also introduces runtime overhead due to runtime compilation and compilation error management.

More importantly, though, there are devices such as FPGAs, which cannot be efficiently programmed using OpenCL—to generate an efficient FPGA implementation, the source code usually requires extensive modifications (manual or automatic code rewriting) to make it suitable for hardware synthesis. In some cases, specific hardware implementations need to be provided in a hardware definition language (HDL). This makes FPGA synthesis difficult to integrate even with traditional software build process, let alone with runtime compilation employed by OpenCL.

In FitOptiVis, the consortium is developing a new OpenMP offloading methodology which explores solutions to these limitations. The new approach, presented in the following sections, is based on two main techniques: source-code offloading and dynamic code management at runtime.

# 4.3.1 OpenMP Offloading Requirements

To support the new offloading methodology, the runtime implementation developed within the consortium aims to meet the following requirements:

- During compilation, the compiler should include in the executable files the code of the threads that could be allocated in different computation resources at runtime.

- There should be a methodology that allows developing new thread implementations after compilation, but before application execution. The methodology allows extracting the thread code from the executable file and defines mechanisms for dynamic loading of the new implementations.

- During execution, the runtime infrastructure should identify all the available thread implementations. The new implementations will be dynamically loaded.

- The runtime infrastructure provides dynamic thread allocation during application execution.

Page 24 of 118

- The runtime library provides information about the available thread implementations and well as identified computing resources.

- The computing resource information could optionally include performance data, such as memory size and clock frequency.

- The device-specific implementation of a thread could optionally include performance data, such as memory requirements, execution time or power consumption.

- During code execution, the runtime library provides a methodology to facilitate thread runtime monitoring.

## 4.3.2 OpenMP Offloading Methodology

The goal of the consortium is to develop an OpenMP extension meeting the above requirements. So far, we have provide a runtime library that is capable of satisfying the following requirements:

- The runtime infrastructure can detect and dynamically load implementations of target code that were developed after the original code compilation.

- The runtime library provides basic monitoring of thread execution.

- The device-specific implementations can provide performance data for the runtime, which is then used to select the optimal implementation to execute.

In addition, we have been working on the compiler driver of an open source compiler (clang/llvm) to satisfy additional requirements that were not the sole responsibility of the runtime library, such as the inclusion of target code for different resources in executable files, or the development of the code extraction system. To comply with these requirements, we first modified the Clang compiler driver, but due to tight API bindings between the compiler driver and the Clang code generator, we had to use a different approach for code extraction.

The new approach is based on exploiting the capabilities of the LLVM framework to create an automatic code transformation tool that can directly modify the existing OpenMP code for device offloading as well as integrate the new dynamic runtime library. This approach integrates the automatic extraction of OpenMP thread code, the integration of other runtimes such the FitOptiVis dynamic runtime library, and the infrastructure to implement the target code extraction tool.

The code transformation pass needs to satisfy the following requirements:

- It must maintain code functionality, because it is only slicing the parts that define the target thread code.

- It should automatically include any additional files required by a specific target, as well as add any function declarations required after slicing and retooling of the code

- It should generate code from which an OpenMP compiler can automatically build an executable.

- It should be integrated in our modified compiler toolchain, performing code transformation and compilation without extra intervention from the user. The compilation process is therefore split into two phases: modification of the OpenMP code and subsequent compilation.

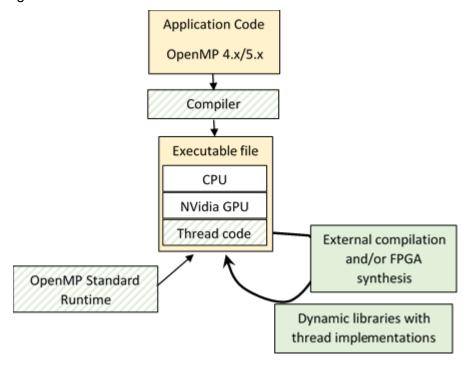

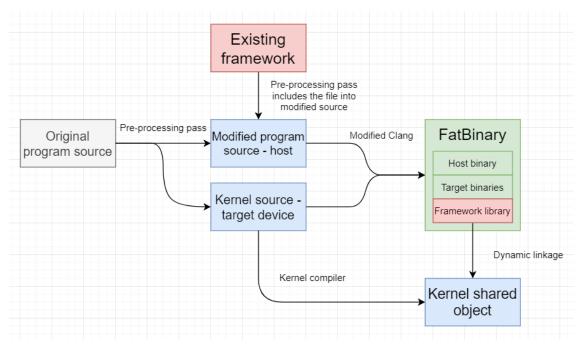

## 4.3.3 The OpenMP Framework

We have been extending the standard OpenMP methodology to meet the above defined requirements in order to support a new target: the thread source code.

We provide a dynamic library to enable integration of our extension into application code. The use of the library is complemented with a code pre-processing pass that will slice and extract the target code. It also automatically provide runtime support for the dynamic library. During execution, the runtime identifies available implementations and allows selecting the desired implementation of the current thread.

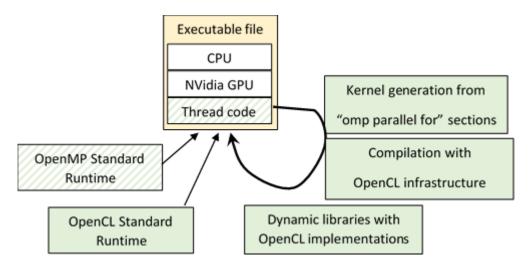

The extended OpenMP framework is shown in Figure 4. The framework currently supports the activities shown in the solid-green boxes, which implement the dynamic thread-implementation management at runtime. The compilation pass embeds the thread source code in the OpenMP executable. An extraction tool can access this code in order to use a different compilation process. The new target implementation is compiled into a dynamic library that is loaded at runtime. The runtime uses an environment variable to discover the newly produced thread implementation libraries and loads them using infrastructure code that was automatically generated by the code extractor. For this reason, all implementations include a common infrastructure that allows identifying the OpenMP thread that the target implementation provides. The OpenMP applications can also access this infrastructure, which allows reconfiguring the thread target allocation at runtime.

Figure 5. The Extended OpenMP framework.

# 4.3.4 OpenMP and OpenCL Integration

The methodology presented in the previous section has been extended to implement OpenMP threads in OpenCL, so that it fits on top of the OpenCL-centric runtime stack described in Section 4.2.

To this end, we generate an OpenCL kernel from the OpenMP thread code sections during code transformation, together with a library that synchronizes the OpenMP thread management and the OpenCL-based resource control. During execution, the application can select the OpenCL device that will execute the thread code, which is then compiled at runtime using the OpenCL API.

Figure 6. OpenCL integration in the OpenMP infrastructure.

This integration has the advantage of adding support for remote-device infrastructures, such as pocl-remote presented in Section 4.2, as well as any other remote device implementations.

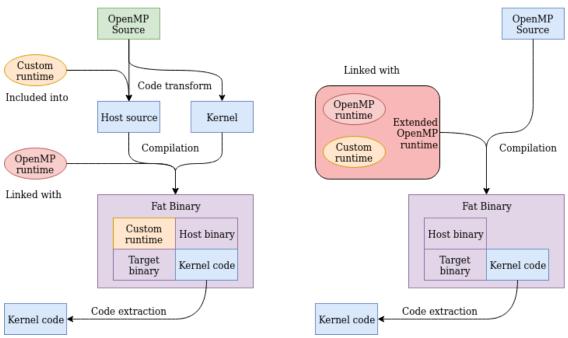

# 4.3.5 Offloading OpenMP threads in a video pipeline

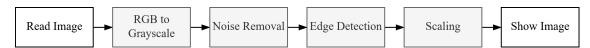

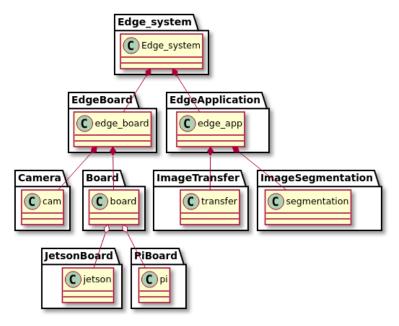

To demonstrate the methodology, we have developed a working example of a video pipeline, which is similar to a pipeline found in UC10, where this approach will be used. In this deliverable, we present a simple example of real-time edge extraction pipeline in which some of the OpenMP threads are offloaded to different hardware resources.

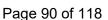

The pipeline, shown in Figure 6, consists of a camera component, which captures and relays images, a compute component, which performs scaling, filtering and edge detection on the images, and a display component, which provides the user with a side-by-side view of the original and the processed images. In particular, the compute component comprises four sub-components: a grayscale filter, a median filter, an edge detection algorithm, and a scaling algorithm. These sub-components were implemented as kernels that can be offloaded to different computing devices.

Figure 7. Architecture of the image processing pipeline (with the compute components in gray)

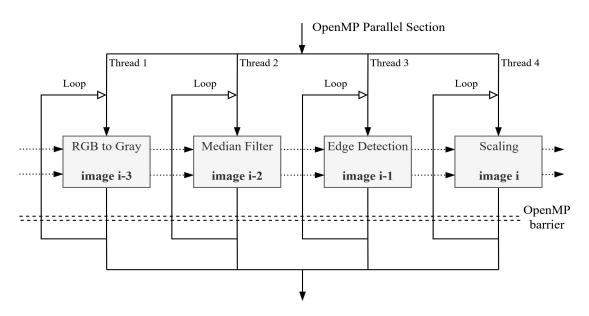

To implement this video pipeline, two OpenMP parallelization strategies were used:

- 1. Parallel section based parallelization.

- 2. While loop with OpenMP tasks and resource control with semaphores.

The first approach (parallel sections) is shown in Figure 7. Every thread (kernel) is implemented in an OpenMP parallel section that is executed in parallel with other sections. Each thread has an internal loop that allows maintaining the video pipeline and a barrier for synchronization with other threads. In this implementation, the video frames are transferred from one thread to another after barrier synchronization. This implementation is close to the UML/MARTE component model that has been developed in WP3, which is why we discuss this implementation in more detail.

The second parallelization strategy provides similar results. It only has an execution path (the video pipeline) which is concurrently executed by several threads. The threads use semaphores and critical sections to avoid resource access conflicts. For example, if four hardware threads or cores are allocated to execute the video pipeline and there is only one camera, only one thread will be allowed to access the camera in a particular time slot. The synchronization on resources causes the threads to execute in a pipeline fashion. The code in the critical sections could be offloaded to different target devices.

Figure 8. Image processing pipeline based on OpenMP parallel sections

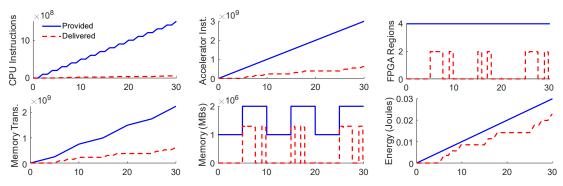

Once the architecture was set, a reference CPU-based implementation was developed and profiled in order to find the bottlenecks in the system. We found that the edge detection algorithm requires more execution time than the other components. For this reason, we have explored two target offloading approaches: GPU-based implementation executed on a traditional PC, and an FPGA-based implementation executing on a Xilinx Zyng MPSoC.

For the GPU-accelerated architecture, an OpenCL kernel was generated and compiled using the standard OpenCL runtime compilation mode. For the FPGA-accelerated MPSoC, the extracted kernel code was heavily modified to take advantage of the Vivado HLS FPGA synthesis tool. Both implementations provided substantial throughput gains, as shown in Table 1 and Table 2.

Table 1 shows the frame rates achieved for a sequential CPU-only implementation, a standard OpenMP-based parallel implementation (which uses four threads executing on

four CPU cores), and a GPU-accelerated implementation (which offloads the heaviest thread on the GPU and executes the three remaining threads on three CPU cores).

Table 1. Pipeline speedup on Intel CPU + NVidia GPU

# OVERALL PERFORMANCE ON PC - INTEL CORE 17-3610QM CPU + NVIDIA GT630M GPU

| Implementation              | Frame Rate | Speed-up |

|-----------------------------|------------|----------|

| Serial (CPU-only)           | 1.60 FPS   | x1.0     |

| Parallel (CPU-only)         | 1.84 FPS   | x1.2     |

| Parallel + Offloading (GPU) | 15.31 FPS  | x9.6     |

Table 2 shows the results of executing the pipeline on the Xilinx Zynq MPSoC with FPGA offloading.

Table 2. Speedup results on Zynq MPSoC CPU+FPGA

#### OVERALL PERFORMANCE ON XILINX ZCU102 - ZYNQ MPSOC ARM CORTEX-A53 CPU + FPGA

| Implementation               | Frame Rate | Speed-up |

|------------------------------|------------|----------|

| Serial (CPU-only)            | 0.92 FPS   | x1.0     |

| Parallel (CPU-only)          | 1.13 FPS   | x1.2     |

| Parallel + Offloading (FPGA) | 21.36 FPS  | x23.2    |

We also want to highlight the need for device-specific optimization when using automatic hardware synthesis tools. If such tools are simply used on the extracted kernel code, the performance achieved by the synthesized hardware is far from impressive. However, after significant code modifications (with hardware synthesis in mind), the generated FPGA hardware can provide tremendous speedup.

This is illustrated by results in Table 3, which shows a side-by-side comparison of the throughput of two FPGA implementations of the median filter sub-component: one is synthesized directly from the extracted kernel code, while the other is synthesized from code which was heavily modified after extraction.

Table 3. Performance of hardware synthesized from unmodified and optimized kernel code

# MEDIAN FILTER HW IP PERFORMANCE ESTIMATES AFTER HIGH-LEVEL SYNTHESIS

| Input to Vivado HLS | Ordinary C/C++ | HW-oriented<br>C/C++ |

|---------------------|----------------|----------------------|

| Image resolution    | 1920x1080      | 1920x1080            |

| Clock period        | 3.08 ns        | 4.58 ns              |

| Clock cycles        | 360810722      | 2073609              |

| IP throughput       | 0.90 fps       | 105.29 fps           |

### 4.3.6 OpenMP Extension Status

During the first year, the consortium has developed the initial approach and infrastructure to support dynamic thread implementations, and demonstrated the integration of OpenCL into OpenMP.

Throughout the second year, we have made significant progress on slicing and integration of target code into a fat binary executable by leveraging the capabilities of the LLVM/Clang compiler. We have added a pre-processing pass to the compilation in which we analyse the thread code, separate target regions into different files, perform code substitution in the original code, and automatically load our runtime library. This makes the original OpenMP program ready for compilation by any OpenMP-compliant compiler which would generate the executable code.

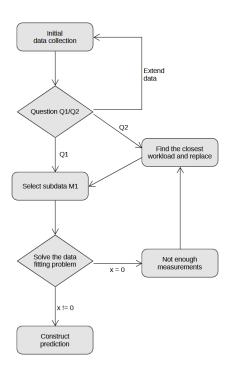

The approach is illustrated on the flowchart in Figure 8. Starting from the unmodified source code, we run the pre-processing executable that will analyse, slice and modify the code to make it ready for compilation. The modified code adds support for the new target offloading style and includes the original target (kernel) source code embedded in string constants.

While this approach has been originally devised for transformations of OpenMP code to OpenMP code, once implemented, the pre-processing pass can be extended to also offload (with some limitations) OpenMP threads to OpenCL kernels.

In comparison, the original approach required modifications and extensions to the Clang OpenMP runtime libraries, extensive modifications of the code generation module of the compiler driver and of the compiler interfaces between the code generation module and the Clang Runtime Library. It also required creating an external tool for code extraction.

While such an approach may have seemed convenient and low on toolchain bloat, it ended up requiring extensive modifications to tightly coupled and not very well documented libraries and APIs. In addition, both the code generation module and the runtime library were specifically designed to adhere to OpenMP 4.5/5.0 specifications. Consequently, it is not ready for device-agnostic offloading or code injection at runtime (after compilation), because the target intermediate representation is generated in tandem with the target region delimitation and outlining.

Figure 9. The pre-processing approach for integrating target code into fat binary

The improved approach aims to leverage the OpenMP code annotation pragmas to direct not only compilation for known targets, but also for unknown targets at runtime, without requiring complex modifications of undocumented LLVM/Clang code. It also simplifies the construction of the code extraction tool, which can then extract target code directly from the source code.

The main difference between the two approaches is how the extra functionality is added. The modifications and extensions to the Clang OpenMP runtime library required by the original approach would need to be accepted into the official Clang code. This would require new API endpoints for the Clang compiler to call to be introduced into the code generator.

In contrast, the improved approach adds the new functionality as an extra runtime library and code to load the library is automatically added during the pre-processing pass. This makes supporting the extensions much simpler, with minimal modifications in the code generator module (to add the source code of target regions into symbols, something requiring very little code and no extra API endpoints). Figure 9 shows where the extra functionality is integrated into the program and where the compiler modifications would occur.

# New approach OpenMP Source

# Original approach

Figure 10. Comparison between the improved and the original approach to extending OpenMP

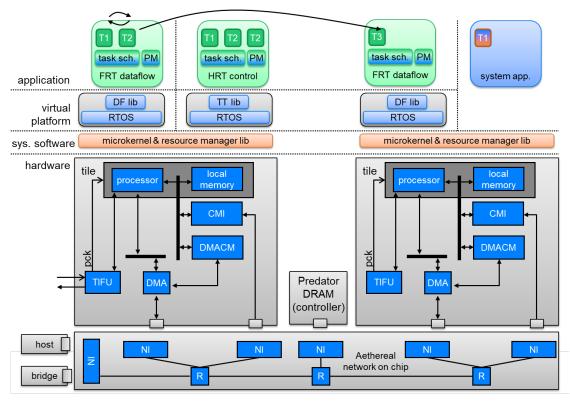

# 4.4 The CompSOC Platform

The CompSOC platform offers a Virtual Execution Platform (VEP) to each application. VEPs are entirely isolated from each other (space, e.g. memory, and time, e.g. TDM on processors or network-on-chip), such that each application can use its own Model of Computation and can be developed independently. This section is a summary of the platform description presented in [GOO17].

#### 4.4.1 Hardware Architecture

MPSoCs contain multiple processors with local and shared memories. The processor's local memories are always on-chip Static Random-Access Memory (SRAM), close to the processor. Nonlocal memories shared between processors may be on-chip SRAM but often include off-chip Dynamic Random-Access Memory (DRAM). The latter has a much larger capacity (number of bits) than the on-chip memory, but at the cost of a longer execution time. Processors reach shared memories using a communication infrastructure, which is increasingly a NoC. A NoC is a miniature version of the Internet in the sense that communication is concurrent, is distributed, and is either packet based or circuit switched. As a result, it can run multiple applications of different criticalities at the same time. The CompSOC platform consists of multiple tiles interconnected by a NoC. Tile types are master tiles, slave tiles, or a mix of both, and include processor tiles, memory tiles, peripheral tiles, etc.

#### 4.4.2 Software Architecture

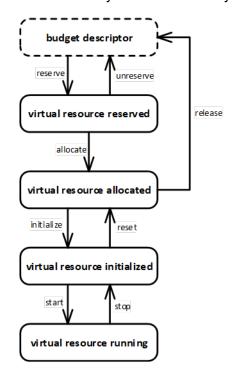

The CompSOC hardware platform contains computation, communication, and storage resources. Almost all can be shared between multiple requestors, and almost all can be (re)programmed at run time. The CompSOC software extends the single hardware platform to offer multiple Virtual Execution Platforms (VEPs). A VEP is an execution platform that is a subset of the CompSOC hardware platform, in terms of time (e.g., time multiplexing a processor) or space (e.g., non-shared DMA or a region in memory). Each application runs in its own VEP, which is created, loaded, started, and possibly stopped and deleted, at run time. A CompSOC platform can run multiple VEPs concurrently, without any interference between them, i.e., composably.

#### 4.4.3 Microkernel and RTOS

Task arbitration can be classified along several axes. First, it may be absent when there is only one task on a resource. Otherwise it is required. Second, it may be preemptive or not. Third, arbitration may be static and follow a static-order schedule or be dynamic where the order of tasks is determined at run time. Multiple applications can share the processor using a microkernel such as CoMik, which arbitrates only between applications. Each application can use virtualized RTOS, such as  $\mu$ C-OS III, to independently arbitrate between application tasks.

An example CompSOC platform is shown in Figure 10 [GOO17].

Figure 11. An example CompSOC platform.

Page 33 of 118

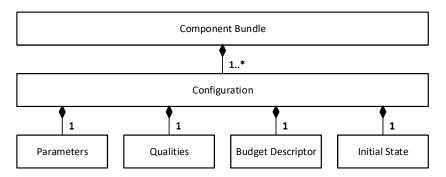

## 4.4.4 FitOptiVis QRM Framework on CompSOC

The above CompSOC platform will be used to implement quality and resource management (QRM) framework envisioned in FitOptiVis. This requires several further developments including the dynamic reconfiguration mechanism and budget handling in line with what is developed in WP2. Further details of these platform adaptations are provided in Deliverable D4.3.

# 4.5 The Xilinx Zynq Platform

In contrast to the predecessor ALMARVI project, which only provided support for standalone boards and no board-to-board communication, the FitOptiVis project focuses on providing Peta Linux and Debian OS support, as well as enabling board-to-board communication in a local cloud.

The first version of design time and runtime support for the family of Xilinx Zynq and Zynq UltraScale+ systems has been developed by WP4 partners and released for use by project partners and general public by the end of April 2019. The new runtime provides support for Ethernet-based board-to-board communication in the local cloud, utilizing the Arrowhead framework, which is compatible with C/C++ clients running on ARM processors.

The following Xilinx Zynq systems are supported:

**ZynqBerry (small)**. A small-size, low cost system with design time support developed in FitOptiVis. It has the Raspberry form factor and utilizes a 32bit Xilinx Zynq device (28nm) with small programmable logic area. WP4 provides support for Arrowhead-based board-to-board communication, Debian OS, and 32bit C/C++ clients. See [KAD18a], [TE0726], and [ARROW] for details.

**Zynq UltraScale+ (medium)**. A medium-size system with design time support developed in FitOptiVis. Utilizes a 64bit Xilinx Zynq device (16nm) and reuses the carrier board and the Full HD video I/O FMC card from the ALMARVI project. WP4 provides support for Arrowhead-based board-to-board communication, 64bit Debian OS, and 64bit C/C++ clients. See [KAD18a], [KAD18b], [ARROW], [TE0820], and [TE0701] for details.

**Zynq UltraScale+ (large)**. A large-size system with design time support developed in the FitOptiVis. The carrier board has the Mini-ITX form factor, utilizes a 64bit Xilinx Zynq device (16nm), and reuses the Full-HD video I/O FMC card from the ALMARVI project. WP4 provides support for Arrowhead-based board-to-board communication, 64bit Debian OS, and 64bit C/C++ clients. See [KAD18a], [KAD18c], [TE0820], [TE0808], and [TE080X] for details.

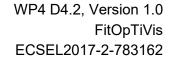

# 4.6 Deterministic Networking Platform

Time Sensitive Networking is a set of IEEE 802 standards providing reliability and determinism in Ethernet networks, which is required by time-sensitive applications. TSN enables mixed-criticality communication by allowing real-time and best-effort traffic to coexist on the same network infrastructure.

Page 34 of 118

TSN is committed to standards that are fully integrated into the Ethernet protocol stack, as virtually all the functionality belongs to the IEEE 802.1 bridge layer—except the frame pre-emption capability, which is developed on top of the IEEE 802.3 MAC layer.